单面PCB布线阻抗的工程设计。碎片三分钟,收获一丢丢。

此课题来源于一次直播过程的学员提问,当时没回答,因为三言两语讲不清楚。

大概率您会这么想:

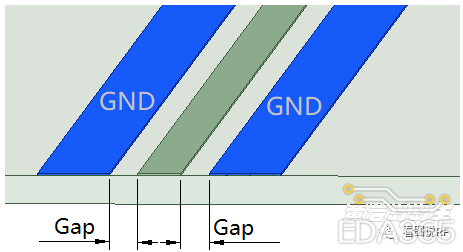

单面PCB,没有地平面,采用双侧都有地线的共面波导结构,就能实现布线阻抗控制:

想得美,理论丰满,现实骨感。

能想到用单面PCB实现布线阻抗控制的老板,一定在物料成本上考虑到了极致:

与常规双面PCB相比,单面PCB少了过孔金属化、背面铜蚀刻、背面丝印、背面绿油等工序,减少了PCB制造成本;

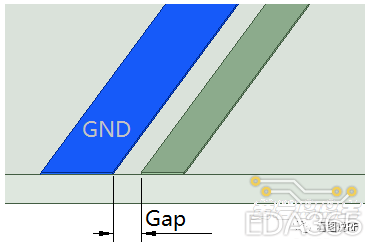

单面布线面积也一定会尽量减小,两侧铺地增加了布线面积、增加了布通难度,所以只能单侧铺地(跟随地线)。

那么,单侧铺地的阻抗由铺地间隙Gap大小决定?

那又单纯了,典型的没经过社会拷打。

能想到单面布线阻抗控制的老板,一定会找个极低成本的三线PCB厂家加工,别指望线宽(等同于线间隙Gap)加工精度了。这种三线PCB厂家只保证基本的通断。

单侧铺地的Gap与阻抗关系

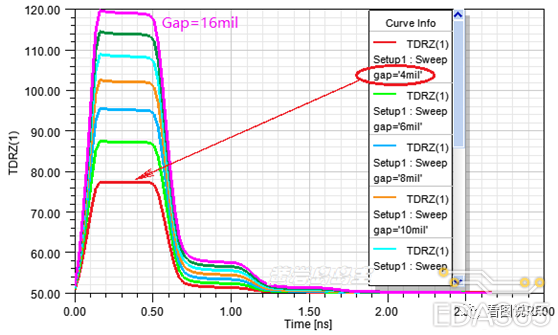

为了让大家死心,特意用HFSS建模,FR4介质厚度20mil,铜厚1.4mil,线宽30mil。看一眼单侧铺地的Gap与阻抗关系:

看一眼单侧铺地的Gap与阻抗关系:

30mil线宽单面布线,铺铜间隙Gap=4mil(主流PCB厂家普通制造工艺能加工的铺铜间隙),阻抗也只能做到77欧,与50欧相差太远。

铺铜间隙Gap=4mil大概是主流PCB厂家能保证通断能力的铺铜间隙,实际加工出来的Gap可能3~5mil范围,有+/-1mil误差是很正常的,会导致阻抗控制误差超过20%。

即使如此,别指望低成本的三流PCB厂家也能加工出4mil铺铜间隙。

上图的紫色线,对应铺铜间隙Gap=16mil。

解决方案

根据公式Z0 = sqrt(L0/C0),增加单位长度的电容量,就能降低阻抗到50欧。

单位长度,是指远小于导波波长的长度。

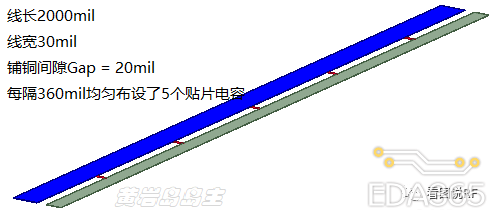

单位长度的电容量,用均匀排列的贴片电容实现。

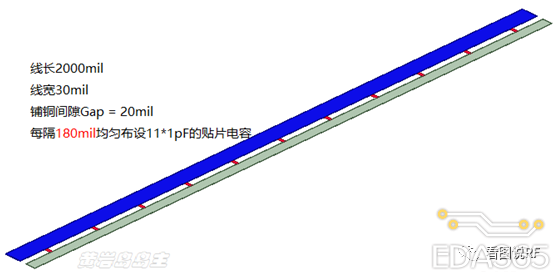

下图模型:

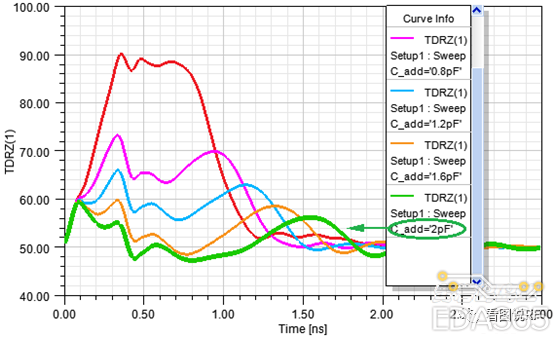

仿真出来的阻抗如下:

红线0.4pF,TDR曲线显示的阻抗88欧;

绿线2pF,TDR曲线是最接近于50欧的;

说明这个长度2000mil的布线结构,需要用贴片电容增加总共5*2 = 10pF左右的附加电容,才能将阻抗压到50欧左右。

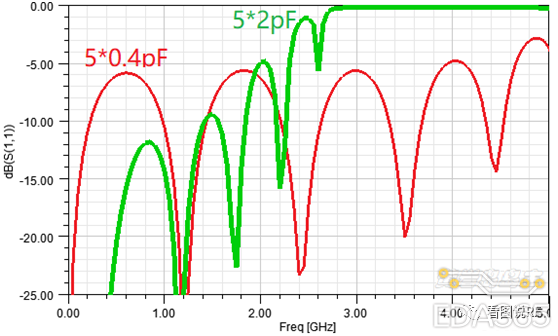

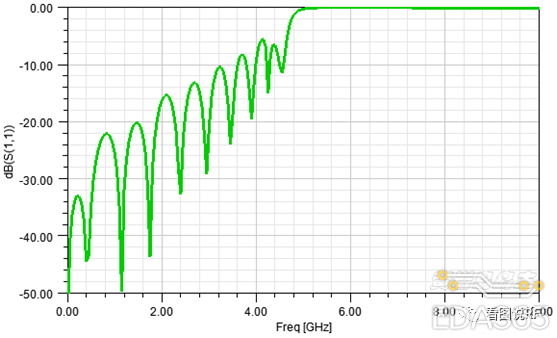

看看回波损耗:

对于数字电路,假设以回波损耗10dB为限:

5*2pF拓朴结构,大致能传输1Gbps信号。

5*0.4pF拓朴结构,大致能传输0.15Gbps信号。

还是有收获的。

单位长度减半

下图模型:

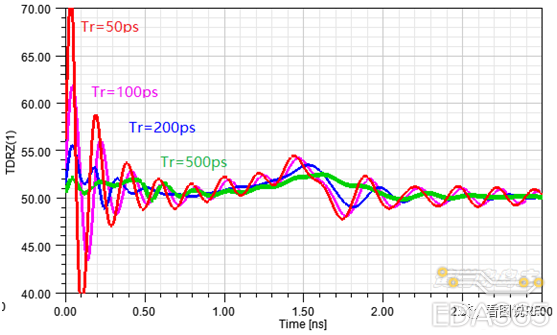

看看上图拓朴结构的TDR瞬时阻抗,与上升沿Tr关系:

蓝线阻抗大致控制在+/-10%,对应上升时间Tr=200ps。

绿线阻抗大致控制在+/-5%,对应上升时间Tr=500ps。

再看看回波损耗:

按照前面假设的标准,每隔180mil布局1pF电容,大致能传输2.2Gbps数据信号。

本文的模型,用了HFSS的LumpRLC边界条件,这与实际的贴片元件仍然有分布参数的差异,低频率时误差不大。

总结

共面波导结构理论上能实现单面PCB布线的50欧阻抗控制,但实际工程上是很难实现的:因为要求铺铜间隔Gap小于4mil。

可以采用大的铺铜间隔Gap=20mil,但每隔单位长度布局贴片电容的办法实现50欧阻抗控制:

每隔360mil布局2pF电容,大致能传输1Gbps数据信号。

每隔180mil布局1pF电容,大致能传输2Gbps数据信号。

依此类推。

电容间隔总不能小于封装本体吧?因此,这种拓朴结构只能用于低频低速信号。

出品|EDA365

作者|何平华老师

注:本文为EDA365电子论坛原创文章,未经允许,不得转载

- 还没有人评论,欢迎说说您的想法!