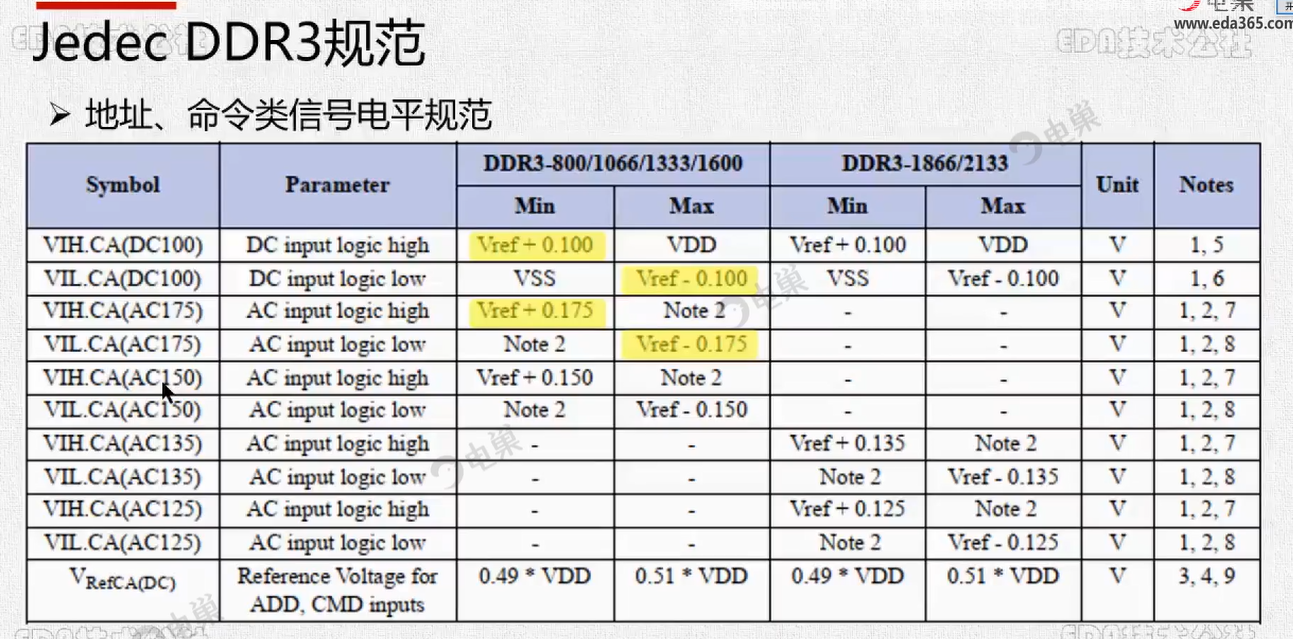

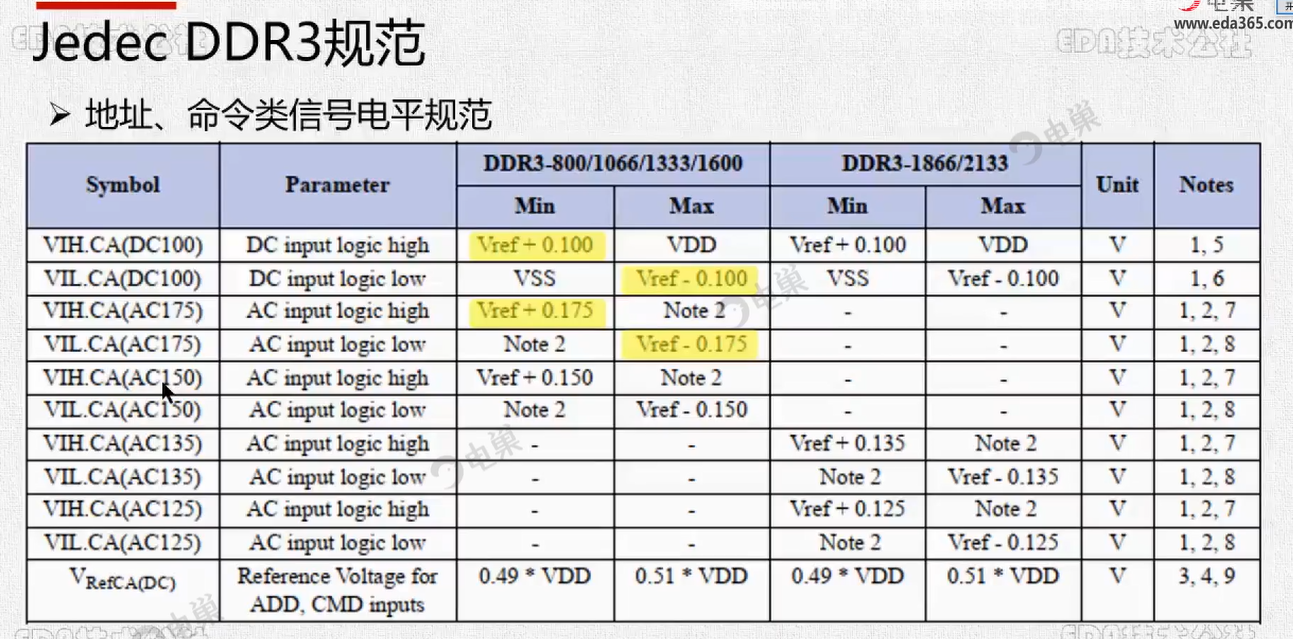

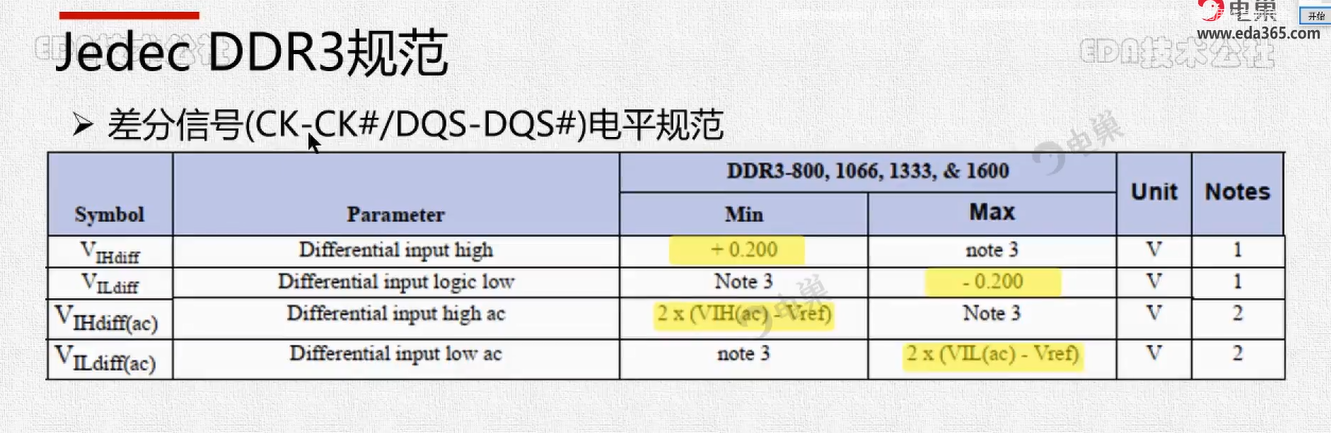

Jedec DDR3规范。

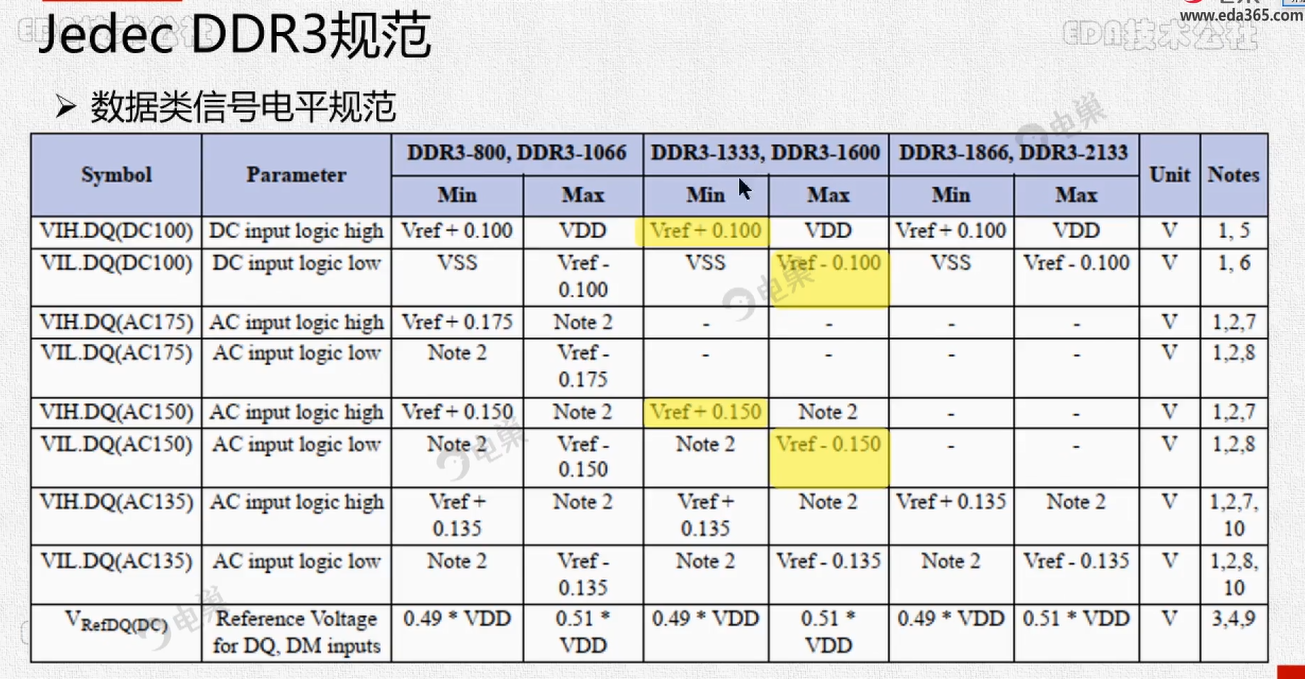

Jedec DDR3规范。

不能播放

General SI simulation (ideal p/G)

终于学完了整个课程,记了两个笔记本的笔记,项目操作也越来越熟练了!跟工作中做过的项目有一些重叠,更多的还是学到了新的知识!

即将开始自己的新工作,做一名合格的SIPIEMC工程师,希望在新环境中能够更进一步!

爱杜老师,爱陆妹巢妹,爱电巢,爱EDA365!

目前ddr几G内,这个软件已足够使用

信号上升时间大约为一个ui的1/4

ui和信号周期的关系?

ddr3地址信号:

A0-A14,BA0,BA1.BA2,CAS,RAS,

1>检查叠层:

1.各个层的厚度

2.传导率(只有铜有),使用默认的

2.各个材料的介电常数

3.介质损耗

4.横截面

5.铜箔粗糙度

2>焊盘的参数(一般做dc仿真时用的比较多)

3>信号勾上次才会进入仿真的范围,差分线选择一根,其他另外一根也会选择

4>差分线么有分配+极,右键classify-auto assign polarity,(批量操作?——全选中右键自动分配)

1.si积分?

2.串扰积分?

3.信号积分?

4.信号相对比理想的信号为什么是没有串扰的信号面积减去si减去串扰的积分,不是应该是正常情况下的信号(加串扰信号的信号)-si-串扰积分嘛?

5.性噪比?

方案不错万亻6好好我们的世界如此美好却不能

明,至几哈里路业is L