3月12日【电巢直播间】《用数据说话—HFSS仿真实操案例讲解第二期》——答疑

直播回看地址:https://edu.eda365.com/my/course/65

问题一:这里Q值定义是?

Q值就是传统的定义,处于最低自谐振频率的屏蔽腔,等效于LC并联谐振电路。所以屏蔽腔最低自谐振频率的Q值,也等效于LC并联谐振电路的Q值,例如Q值等于振荡能量与损失能量之比。

我们看到本征仿真的自谐 振频率Q值也有100左右,看起来Q值也不低,但是屏蔽腔毕竟不是谐振腔,内部的PCB和元件不能正好形成合适的加载结构,所以Q值100的本征模式是谐 振不起来的,所以不用关心。根据仿真经验,我们要关注那些Q值超过1000的自谐振频率。

问题二:为什么缝隙越大,隔离度越大?

因为屏蔽盖缝隙越大,屏蔽腔就会越开放些,开放的屏蔽腔会对外辐射能量,会降低自谐振的Q值,Q值会降到谐振不起来的适度。

我们的前两步的仿真模型中,已经证明了屏蔽腔内部隔离度与自谐振密切相关:本征模式仿真的高Q值自谐振频点正好是隔离度劣化尖峰频点。

所以缝隙越大,自谐振Q值越低,腔体越不容易谐振,那么隔离度就越高。

问题三:请问Q值怎么定义呢?阻抗虚部除以整部?为什么Q 值高频率选择性高?

谐振电路(或谐振结构)的Q值都是一样定义的。

Q值就是传统的定义,处于最低自谐振频率的屏蔽腔,等效于LC并联谐振电路。所以屏蔽腔最低自谐振频率的Q值,也等效于LC并联谐振电路的Q值,例如Q值等于振荡能量与损失能量之比。

这位网友问的都是基本理论,建议网友自己找相关资料学习,书上讲的肯定比何老师回答的更精确。

问题四:结构越小自谐振频率越高吗?

那当然是。

无源射频微波电路有等比例缩放的特点。3D结构尺寸等比例变化,则特征曲线在频率轴上等比例平行移动。

问题五:改如何增大近场磁场,而减小远场(四分之一波长以外)的辐射?

没有描述清晰的场景,所以网友的这个问题无法回答。

问题六:带孔缝的腔体能仿真自谐振频率吗? 用本征模求解?

能仿真啊。

对,是用本征模求解。

但要设置好模型的边界条件,要与真实情况一致,否则仿真结果是不对的。

如果能量会从孔缝辐射出去,那么就要在外面罩个较大的六面体空气盒,并将空气盒的六个面设置为辐射边界条件(吸收边界条件)。

问题七:射频功放板也是有这种模型仿真吗?

HFSS只能仿真无源电路,所以只能仿真没有电源的功放板。

HFSS无法仿真有源电路,因此不能仿真功放板的有源参数,如功率、失真等。

3月14日【电巢直播间】《控制系统架构与CPU技术概述》——答疑

问题一:UFS读时钟,大概在什么频率?

目前的UFS3.0标准,采用M-PHY 4.1 物理层,采用8b/10b编解码的串行线技术,物理层理论速率可达到23.2 Gbps (2.9 GB/s),实际吞吐量可达到15 Gbps (1.875 GB/s)。

问题二:现在IC都是CMOS工艺还是TTL工艺?

数字电路芯片CMOS工艺居多,因为CMOS工艺相对TTL工艺,相同的规模下,节省硅片资源,另外,CMOS工艺同等条件下的功耗也比TTL工艺低很多。

问题三:RISC-V有什么芯片?

建议关注下SiFive公司,它有一系列RISC-V的CPU芯片和IP。另外,国内有华米的黄山1号,用于穿戴产品;阿里平头哥的玄铁910,可用于边缘部署的AI 设备中,实现推理功能。

首先是在实际工作实践中积累设计经验,解决问题,每一次解决问题的经验都是极其宝贵的,最硬件工程师的成长非常重要。硬件工程师一定要会编程,至少是嵌入式底层软件,要能够独立设计和调试测试,对工程师全面了解CPU工作和电路工作原理非常重要。其次是要关注硬件周边及行业的动态等,硬件是个技术范围很宽的岗位,需要工作电路板周边的各个DFX环节,如工艺,SI,EMC,可靠性等等,这样才能成为一个独当一面的工程师。

问题五:请教,主频1G 四核,是每个核1G么?

是的。

问题六:作为CPU硬件工程师,有哪些资料推荐学习的?

个人觉得最重要的是学习IP厂家或CPU器件的资料,如ARM,Micron,SiFive等等,通过阅读厂家的资料可以学习到很多知识,如CPU内部架构,DRAM原理等等,还可以学习到设计技巧等。另外可以在国外的网站上搜索一些和CPU相关的视频看看。

问题七:老师帮忙推介下看哪些国外网站可以看?

https://developer.arm.com/:ARM的开发者网站。

https://www.micron.com/:Micron官网,有关Flash 和DDR RAM的器件资料很全。

https://www.anandtech.com/: CPU系统综合类技术网站

https://mipi.org/:移动设备接口技术网站

https://www.youtube.com/: 好东西很多,自己搜索。

问题八:老师您好,您觉得硬件工程师的话,对于一个新人,模拟,强电电力电子类,数字,集成类,RF,高速低速,或者其他类,钱途上来看的话,哪个更贴切目前及未来的发展方向?谢谢老师

这个问题很大,涉及到个人前途问题,我也不敢擅自表达。从我自身的经历来看,一个电路系统其实各个模块都是不可或缺的。中国经过这么多年的发展,工程师资源还是相当丰富的,但在模拟,射频,高速方面仍然和国际领先水平有较大差距,有志向的同学可以往这方面发展。

3月17日【电巢直播间】《20年,三块板-一个硬件工艺工程师成长历程》——答疑

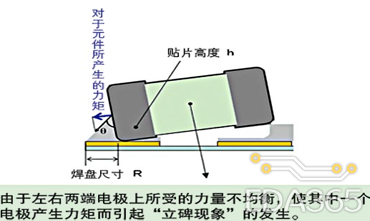

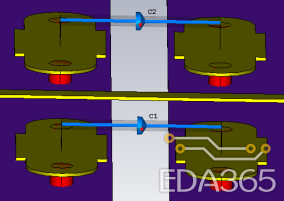

问题一: 焊盘设计成什么样才有立碑现象?

答:焊盘与物料焊端两侧受力不均衡会产生立碑,另外焊盘两侧铺铜及引线不平衡也会导致热容量不一致,再者注意SMD、NSMD及半阻焊定义三种设计。5 f7 R+ y8 z9

答:焊盘与物料焊端两侧受力不均衡会产生立碑,另外焊盘两侧铺铜及引线不平衡也会导致热容量不一致,再者注意SMD、NSMD及半阻焊定义三种设计。5 f7 R+ y8 z9

W9

(~# Q& K( X/ a9 g+ r1 C

问题二: 大陆哪四大工艺能力板厂?

答:沪士、生益、深南、惠亚(TTM)

问题三: 来晚了前面没听到,大焊盘阻焊开窗对散热有作用吗?不上锡也可以散热?

答:有作用、通过散热焊盘将热传递到PCB铜层,不上锡会影响散热

问题四: 焊盘的过孔是要离焊盘一定距离吗?那阻焊桥怎么做?

答:最小阻焊间隙、最小阻焊桥宽、最小覆盖扩展尺寸,取决于阻焊图形转移的方法、表面处理工艺以及铜厚

问题五:怎么根据器件多少预估工艺质量?

答:要构建器件级的质量数据库,根据器件在历史单板上的DPMO对新单板进行直通率预计

问题六: 大板的翘曲问题产生原因、怎么避免?

答:IPC对于线路板变形有两种情况定义,一是弓曲(Bow);二是扭曲(Twist), 其可接受标准是:

通孔安装焊接后的板=《1.5%;表面贴装焊接后的板=《0.75%;

1.PCB设计:PCB板的层压结构、材料类型已经图形分布是否均匀,直接影响了不同芯板以及铜箔之间的CTE差异,在压合过程中的涨缩差异会通过半固化片的固片过程而被保留并最终形成PCB板的变形.在PCB设计时,叠层结构要考虑到尽可能选用类似CTE系数的材料。PCB设计叠成结构中,铜箔厚度,介质厚度必须要对称。

2.PCB板加工:PCB板加工过程的变形原因非常复杂可分为热应力和机械应力两种应力导致。其中热应力主要产生于压合过程中,机械应力主要产生板件堆放、搬运、烘烤过程中。

3.PCBA组装过程: 在SMT过程中,回流焊和波峰焊工序也会引起PCBA板变形

a.温度曲线要符合要求,尤其是升温和冷却率应该得到严格控制

b.炉内轨道宽度是否得当,是否有外力卡住线路

c.使用载具,适当的固定方式控制PCBA变形

d.出炉后,线路板应平放在周转盘,尽可能不立放在周转架上。

问题七: 散热焊盘开窗孔还可以塞孔吗?0 x: K" |( k' v( m6 A* L/ [

答:结合应用场景有些是可以塞孔的,如金属衬底板

3月18日【电巢直播间】电源器件测试建模让仿真更便捷》——答疑

问题一: 电源模型类产品(将一颗电源芯片和若干阻容和电感器件封装在一起)做联合仿真时,提供封装的RLC参数做联合仿真好,还是提供封装的S参数或Hspice模型做联合仿真比较好?

答:这个问题的回答,参考个人的工作经验及对仿真的理解,回复如下:

1) 电源模块类仿真,是属于系统电路级别的,电路系统的仿真软件用Saber,这个在行业中进行系统的比较少;实际做的比较多的是局部电路仿真,来确定一个元器件的选择或几个R、L、C元件的搭配是否合适,这个用Pspice、LTspice、SiMetrix比较多,差异是PSpice适用性强、元件库也较多,LTspice库元件主要ADI的电源芯片、模拟芯片等,SiMetrix适用性强,但库元件较少。

2) 就提到的问题表述来看,选择RLC参数做联合仿真较好,因为S参数是进行射频、微波类器件仿真的,非电源类;而HSpice主要是用于芯片仿真的,用作电源仿真比较少。

问题二: 模型通常在哪里下载?

答:PSpice软件包括的模型库很多,大多数厂家的都有;关于元器件模型库,行业现状是美系、欧系厂家网站上基本都有其PSpise、LTspice、S Parameter、altium、CADStar、Eagle等模型;日系、韩系、台系厂家个别网站有元器件库模型,大多数没有;国产厂家基本上没有元器件模型库,极个别资深工程师可以建模,在有业务往来时可通过沟通获取模型。

问题三: PSpice不收敛,怎么处理?

答:若遇到此仿真不收敛问题,建议如下:

首先、审视元器件模型,是否与实际测试无线逼近;

其次、看下选择的电压源、电流源、负载与实际电路的差异,一般需要将其的内置电阻等效出来。

以上两种若还有问题,建议可联系PSpice高手,或者找电巢的专业老师,就具体的问题进行讨论解决方案。

问题四: 米勒效应能仿真吗?

答:米勒电容、米勒效应是与Mos特性强相关的,在下期的PSpice容差容限分析进阶直播课程中,法老师会讲到Mos的特性及米小效应方面的仿真,请持续关注电巢APP和EDA365论坛的最新直播安排。

问题五: PSpice的收敛问题比较多,特别是瞬态分析?

答:瞬态分析是时域仿真最基本的,若问题较多,建议从基础再学习一边,推荐的课程资料如下,参考Page17~19页,若还有问题,可将问题在EDA365论坛上提出,无论是在allegro cadence还是器件选型&认证板块,都有专业老师进行回答的。

& a#

最后,看到各位网友学习的热情这么高,也请大家关注如下从EDA365论坛及行业网站整理的PSpice仿真方面的热帖和资料,会有超出你预期的收获。

6 O7 g9 `* t0 d% l0 s| 论坛热帖或行业参考 | 网址链接 |

| 电源器件建模及局部电路仿真基础之头脑风暴 | https://www.eda365.com/thread-298461-1-1.html |

| 电源仿真软件小盘点 | https://www.eda365.com/forum.php?mod=viewthread&tid=279257&highlight=%B5%E7%D4%B4%B7%C2%D5%E6 |

| 开关电源仿真PSPICE和SPICE3应用 | https://www.eda365.com/forum.php?mod=viewthread&tid=176094&highlight=%B5%E7%D4%B4%B7%C2%D5%E6 |

| PSPICE的高频开关电源仿真实例 | https://www.eda365.com/forum.php?mod=viewthread&tid=182996&highlight=%B5%E7%D4%B4%B7%C2%D5%E6 |

| 开关电源从分析到计算到仿真 | https://www.eda365.com/forum.php?mod=viewthread&tid=305815&highlight=%B7%C2%D5%E6 |

| IBIS模型可视编辑,检查,验证工具。与大家分享! | https://www.eda365.com/forum.php?mod=viewthread&tid=35253&highlight=IBIS |

| 分享 各大公司IBIS下载地址列表 | https://www.eda365.com/forum.php?mod=viewthread&tid=141491&highlight=IBIS |

| Coilcraft电感S参数及SPICE模型 | https://www.coilcraft.com/models.cfm |

| Wurth electronic元器件模型库 | https://www.we-online.com/web/en/electronic_components/produkte_pb/bauteilebibliotheken/libraries.php?_ga=2.95958748.1550222748.1582794482-963531091.1582794482/ |

3月19日【电巢直播间】《PCB布局层叠和布线EMC设计》——答疑

问题一: Wifi陶瓷天线一般放板子长边中间位置,靠两边地的辐射,为什么老师说是放四角呢?

具体问题具体分析。没有图,没有应用场景和尺寸结构等限制条件,就不好做进一步分析。一般来说,地是用于反射天线信号的。

问题二:单侧PA的辐射很小,各次谐波辐射都很小,但是PA经天线馈线到达天线,经天线的辐射发射谐波很大,原因可能是什么?

可能天线馈线质量有问题或者馈线与天线及PA的连接每做好,更换质量更好的馈线或重新安装下馈线再试试。

问题三:有一些接口电路,板内的数字地与接口的外壳地用一个电容和一个电阻连接,这种设计有什么好处,主要用在哪些方面?

这种连接方法对EMC非常不利,板内的数字地应该与外壳多点连接,连接点越多数字地上的地噪声越小,可以有效的减小共模辐射。

有些产品如电力产品、医疗产品出于安全问题或者漏电流考虑,要求功率地或数字地与金属外壳隔离,这时用电容+电子的连接方式,电容用于缓解二者不连接的负面影响,电阻用于防止浮地的静电累积。

问题四:一般接大地与数字地PCB板上要多远?

设备接地线应接到设备金属外壳上,不应直接连接PCB。

问题五:电源上电冲击电流如何解决?

有增加缓启电路的,如-48VDC端口增加缓启电流就可避免插拔大电流而打火;还有端口增加浪涌防护

问题六:信号阻抗不连续可以通过什么方式检测出来?

通过TDR测试。

问题七:对外有信号接口,也需要EMC的要求,如何对信号接口处理?要做隔离吗?

外部信号接口如何是非屏蔽线一般都需要进行滤波设计,线长超过10m要做滤波浪涌防护设计,是否隔离要看端口类型,如网口就一定是隔离的

问题八:启动冲击电流如何解决?

有增加缓启电路的,如-48VDC端口增加缓启电流就可避免出现启动时的大电流而打火

问题九:高速信号跨多个电源该如何解决?/高速信号跨两个电源如何处理?

尽量不要电源分割,如果一定要跨,就需要在分割的电源两边增加缝补电容提供信号回流。

问题十:信号地和大地怎么接?

信号地一般是多点接设备金属机壳,然后机壳通过专门的接地线接大地。

问题十一:模拟地和数字地用OR电阻更好吧,为何说磁珠更好?/模拟地和数字地跨分割用缝补电容还是磁珠好?

模拟地和数字地如何连接比较复杂,不是几句话可以讲清楚的,请上电巢APP 学习我的电子设备设计接地视频公开课

问题十二:除了布板布线EMC,整机EMC还要考虑哪些因素?

结构屏蔽设计、电缆屏蔽设计、整机接地设计等

问题十三:电源环路对EMC影响大吗?

也有大的影响,环路会产生近场辐射耦合到其它电路

问题十四:电源也不考虑单点接地吗?

这问题描述不是很清楚,不是很好回答。是什么样的电源?一次电源模块,二次电源模块

问题十五:多层板在电源层走信号线有什么影响吗?

靠近电源层走线容易造成跨分割,电源噪声也会耦合到信号线上

问题十六:Bob smith电路不要那个接大地的电容行不行?

去掉这个电容,FE电缆里有两对差分线就会悬空,悬空的线容易耦合板内噪声引起造成FE电缆辐射增加

问题十七:单点接地和多点接地要如何选择?

现在电子产品的速率都很高,EMC测试标准也是测试到很高频率,如至少1GHz,单点接地会影响高频辐射的抑制,所以无论是对电路板还是外接电缆尽量避免用单点接地。

问题十八:整机EMC的问题需要注意单板设计吗?

整机EMC问题先从结构、电缆找原因并采取整改措施,如果结构电缆的整改措施代价太高或无法落地,就要从单板EMC上采取措施。

问题十九:PLC电力猫的PCB有没有优化方案?

需要具体的PCB图才能给出改进方案

问题二十:ADC模拟地和数字地分开吗?

答复见问题11

问题二十一:DC电感下面,铜皮都要掏空吗?

DC共模电感下面不应铺地

问题二十二:金属外壳螺丝孔的ESD该怎么处理?

螺钉孔周围需要导电,保证螺钉与外壳可靠搭接

问题二十三:对于塑料外壳的静音怎么处理比较好?

问题描述不清楚,不好回答

问题二十四:差模共模辐射分不清?(怎么区分)

环路引起的辐射一般是差模辐射;信号参考回流面上噪声电压引起的辐射以及电缆辐射都是共模辐射。

问题二十五:RF天线尽量放板子四角,但WIFI陶瓷天线是要放板子长边的中间位置效率是最好!这个怎么解释?因为陶瓷天线需要两边地的辐射?

见问题1的答复。

问题二十六:12层板是5个芯板叠压再加上两层铜皮制成的吗?

这个属于工艺问题,与EMC关系不大

问题二十七:网口接口地和系统地分割,系统地和接口地之间有的会并联一个1NF,有的并电阻,这个是处于什么考虑来选择的?

系统地是什么地?需要更准确的描述

问题二十八:4层板跨分割大多数是底层在电源平面跨分割,如何处理?

低速或电平信号布底层,跨分割问题也不大,当然增加缝补电容更好。

问题二十九:有哪些EMC方面的书籍推荐?

1)Electromagnetic Compatibility Engineering, Henry W. Ott

2)EMC Design Techniques, Keith ARMstrong

问题三十:跨接电容能不能图示画一下,还是有点不知道如何接?

5 h t" b+ j4 d( y

问题三十一:数字信号一般怎么隔离?

变压器、光耦等

问题三十二:谈谈单板 EMC和整机EMC?

1)对于非屏蔽机壳产品,板级EMI性能直接决定了整个产品的EMI性能;

2)对于屏蔽机壳产品,如果板级EMC控制好就可以用较少的结构及电缆屏蔽成本满足EMC要求

问题三十三:EMC的仿真软件是什么呢?

我直播课里仿真用的软件是CST软件

问题三十四:有静磁分布仿真软件推荐吗?

Comsol,HFSS都可以

问题三十五:缝补电容离信号线多远有要求吗?

对于信号线跨分割,建议缝补电容离跨分割处距离不超过250mil

问题三十六:信号线跨分割,对传导测试有影响吗?

如果电源接口布局、布线不合理则信号跨分割对电源口传导发射也有影响; 信号跨分割会引起接地平面共模噪声增加,对信号线传导发射有影响

问题三十七:EFT电容,需要考虑耐压吗?

需要考虑,但也无效用高压电容

问题三十八:缝补电容是并联吗?缝补电容具体电路板怎么放置?

信号以电源平面做参考时会出现跨电源分割情况,这时用缝补电容提供回流,缝补电容跨接在分割槽并连接两边的电源;还有以不同性质的参考面间换参考,缝补电容需要跨接在电源参考平面和地参考平面之间

问题三十九:功率电感的空间传导噪声怎么优化?

功率电感主要应是辐射噪声吧?可以用带屏蔽的功率电感

问题四十:Mipi信号可以串磁珠吗?

要看具体速率多少?串磁珠后需要测试信号完整性

问题四十一:Mipi超标有什么好办法处理?

信号线串磁珠、增加屏蔽等措施

问题四十二:不同平面换参考,打地孔没有用/无效?

不同性质的参考面间换参考,只能增加缝补电容,增加1个或2个EMI抑制效果都不理想,所以要尽量避免不同性质的参考面间换参考

问题四十三:四层板U*2.0走线该怎么走线比较好,如果主U*到HUB再到U*座成环形有什么影响?

需要提供更详细的信息如PCB图才能回答

问题四十四:跨分割对抗阻和EMI,哪个影响更大?

都很大。

3月21日【电巢直播间】《HyperLynxDRC高速pcb设计之SI分析第1期》——答疑

问题一:介绍下目前这些仿真的优势和劣势

答:仿真是针对我们产品的某些性能做一些数据上的预判,来改进电路的性能。优势就是能够减少产品开发的迭代,节省成本。那么如果说劣势的话,我认为一个是仿真模型的准确性会导致判断的准确性,另外仿真相对测试也是有一定的误差。工具方面的优劣势可以参考问题9。

问题二:如何评价抗阻合适?

答:从信号完整性以及电源完整性的影响可以评价阻抗:

1)阻抗突变会引起电压信号的反射和失真,出现信号质量问题;

2)信号线之间的互耦电容和互耦电感形成的阻抗决定了耦合电流和电压的值;

3)串联阻抗的电阻随着频率的升高而加大的损耗衰减,上升边被拉长;

4)PDN的阻抗对电源供电轨道影响较大;

5)返回路径的阻抗会影响产生共模电流的电压。

......

阻抗是连接物理设计和电气性能的桥梁,基于SI和PI方面的影响来评价和改善阻抗。

问题三:射频为什么控制50Ω?50Ω目的由来?

答: RF中通常选用50ohm作为标准有几方面的原因:

1)是功率容量,抗击穿电压与衰减之间的综合考虑;

2)机械美观上的考虑。

同时可以参考EDA365微信公众号的推文

问题四:阻抗越低不是更好吗?为什么不是35Ω?

答:低阻抗是针对PDN网络来讲的,关于阻抗可以参考EDA365微信公众号的推文

问题五:讲讲近端串扰和远端串扰?

答:可以参考参考EDA365微信公众号的推文

问题六:Sigrity仿真咋样?

答:这个问题问的比较简单,我可以简单的回答一下,Sigrity挺好的。

总体来说Sigrity界面友好,仿真速度较快,精度还行。PI的功能做的不多,很适合用来做电源完整性分析,适合新人上手。

问题七:任意拐弯画的类似十度线,难道十度线不好?看仿真结果还不如90度拐弯?

答:10度线本身没有好坏,如果开销大或者成本大那就可以不选择,目前10度走线主要应用于改善玻纤效应。在我仿真的案例中,在一定频率下可能性能不如90度,但在某一范围内还是比90度要好一些。

问题八:HyperLynx仿真软件和HyperLynx DRC仿真软件有什么区别?

答:HyperLynx是Mentor仿真软件的总称,套件中包含三个软件,分别是HyperLynx SI PI Thermol(信号/电源/热仿真)/HyperLynx DRC(自动化电气验证工具)/HyperLynx Adv Solvers(高级电磁仿真工具),两者在概念和功能上有比较大的区别。

问题九:能讲述下几种仿真工具的优缺点以及如何选择?HyperLynx和allegro的交互性如何?

答:1)常用的几种仿真工具有HyperLynx、ADS、Sigrity、HFSS、siwave

2)HyperLynx和Allegro交互非常方便

问题十:仿真入门选择哪种工具更好?/容易入门的仿真工具有哪些?

答:可以参考9中的仿真工具的优劣势比对,没有最好的仿真工具,只有比较适合自己的。“先入为主”影响比较大,可能先接触的工具就会给个人留下一定的好印象。另外可以根据产品的特点来选择仿真工具。容易入门的工具中推荐HyperLynx。

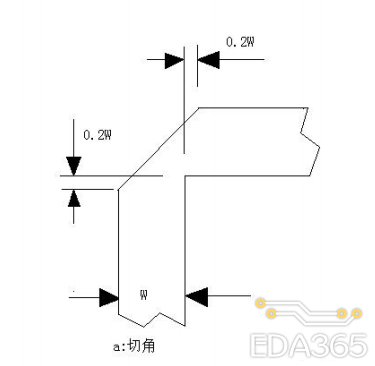

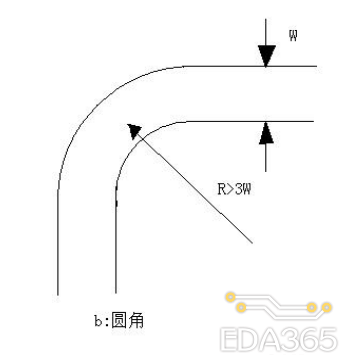

问题十一:对于大功率射频电路,走直角还是走圆角?

答:射频信号走线特别是大功率微带射频电路走线,因为线宽通常会比较大,如果走直角,拐角处的有效线宽会明显增大,阻抗不连续而引起反射。所以通常转角进行处理,主要为切角和圆角两种方法.。

(1) 切角适用于比较小的弯角.切角的适用频率可达 10GHz。

9 f2 X+ v* s* d3 W

(2) 圆弧角的半径应足够大,一般来说,要保证:R>3W。

问题十二:AC电容邻层挖空,那第三层对应区域有必要覆铜吗?那可能会影响第三层布线,是不是第三层不覆铜影响也不大?

答:1)AC耦合电容相邻层挖空,通常参考平面的距离加大,阻抗就会变大,第三层是否要覆铜主要依据阻抗提升的情况来判断,如果挖空第二层参考第三层达到了预期的阻抗,则此时是需要铺铜的,如果还没有达到预期的阻抗,则可以考虑参考第四层或者依次类推。

2)挖空第二层必然对第三层布线有影响,一般建议PCB走线避开挖空区域,避免跨分割,影响信号质量。

如有疑问可前往论坛跟帖回复,我们下期再见!

- 还没有人评论,欢迎说说您的想法!