感谢您使用电巢APP,PC端建议使用Google Chrome浏览器进行观看。

讲师介绍:

杜正阔老师|EDA365 Cadence Allegro论坛特邀版主,原国内知名企业高速设计专家

20多年高速PCB设计、仿真经验。曾任港湾网络、一博科技、兴森快捷等高科技企业工程师、高级工程师、设计经理等职务,设计过的产品涵盖通信、医疗、工控、计算机、雷达、消费类等多个行业

个人主要出版物:

《Cadence Allegro 实战攻略与高速PCB设计》

内容简介

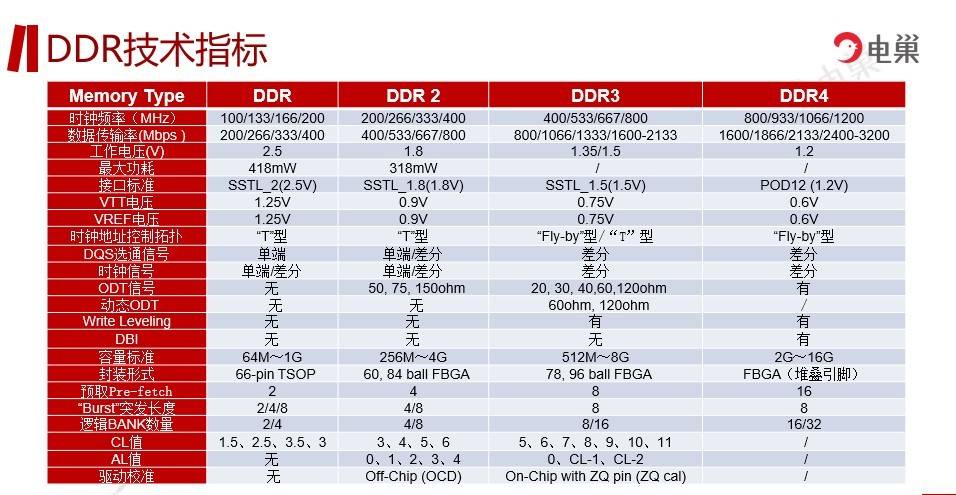

当今电子产品需要进行数据处理的电路架构都是基于冯·诺依曼结构来设计的,包含了运算器、控制器、存储器和输入、输出设备五个部分,存储器又可分为内存储器和外存储器,内存储器可以简单理解为处理器里面的缓存和插主板上的内存,随着芯片的处理能力不断的提高,内存的速度与容量也在不断的提升,每隔几年就会更新换代,如今最新的DDR5规范已发布,最高速率可达6.4Gbps以上,单个存储芯片密度高达到64Gbit,比DDR4的最大16Gbit密度高出4倍,高速PCB设计时,要优先处理好包含DDR模块在内的CPU小系统。明知山有虎,偏向虎山行,只有处理好了DDR模块,才能让系统正常、稳定的工作。

本期直播是《高速PCB设计与仿真最佳实践》系列直播课程的第五课,将分享高速PCB上常用的DDR相关内容,包括DDR特性、设计方法和技巧。加入学习计划的学员还可以通过巢粉引擎的“高速PCB互连设计实训”流程进行对应的DDR模块设计实战,真正把你教会,让你学以致用。

直播要点

DDR特性介绍

DDR设计指南

DDR设计实战

直播收获

了解DDR基本特征

掌握DDR模块设计要求和方法

学会DDR模块设计技巧

适合对象

PCB设计工程师

信号完整性工程师

硬件工程师

电子相关专业学生

电路设计工程师

电子设计工程