课程介绍

讲师介绍:

胡建伟

- 亚太区Mentor EDA分销部门应用工程师经理

- Mentor PCB仿真分析产品技术支持

- EDA行业从业并管理20+年

胡建伟于1999年毕业于东南大学,并获得数字信号处理硕士学位。在高速PCB设计领域拥有丰富的经验和背景,曾任Cadence高级应用工程师,负责支持Cadence PCB设计及仿真工具。

直播介绍:

- 当今电子产品一个很重要的区分元素是其所用的存储器。服务器、计算机、智能手机、游戏机、GPS 以及几乎所有类似产品使用的都是现代处理器和 FPGA。这些设备需要高速、高带宽、双倍数据速率 (DDR)存储器才能运行。每一代 DDR SDRAM(双倍数据速率同步动态随机存取存储器)都会带来新的优势,例如速度和容量的提升以及功耗的下降。要满足速度提升,功耗降低的要求,就要应对设计余量降低的挑战。

- 如何应对挑战不重要,重要的是我们要超车,那就跟着我们学DDRx的仿真!

课程特色:

- 我做:介绍知识背景和我们的练习案例

- 我们一起做:一两个练习,

- 你们课后做:研究其他的练习

直播要点:

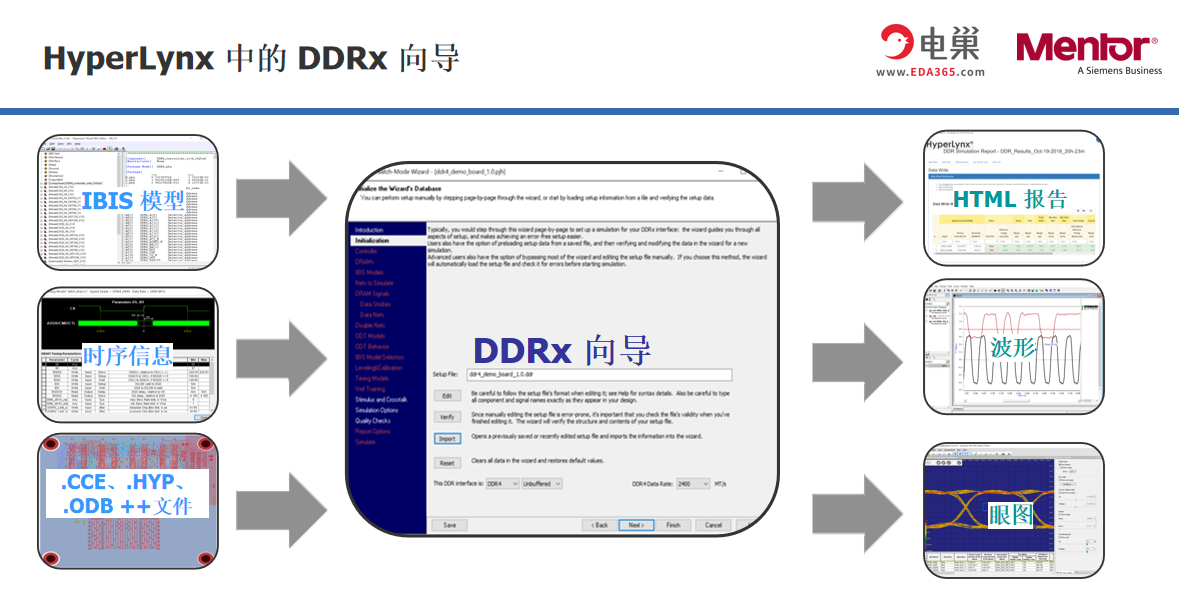

- DDR接口的信号完整性和时序电气规则

- “遵循设计指导布线”为何不再完美

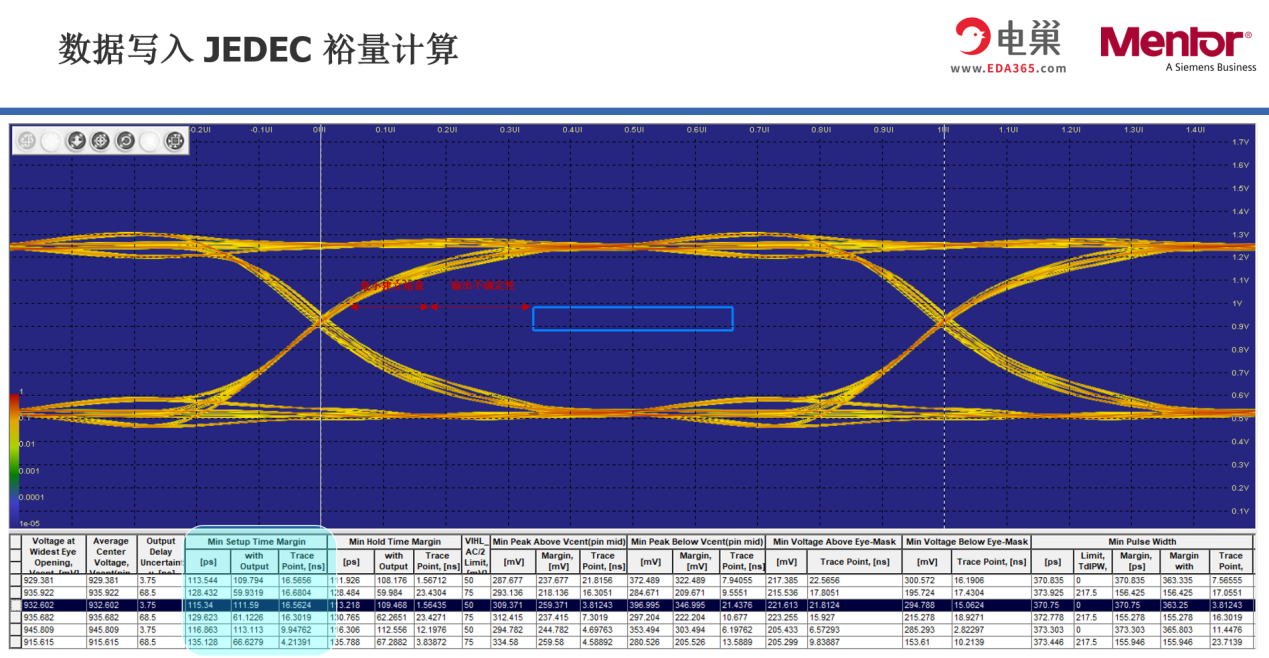

- 为什么JEDEC 规范只能提供验证所需的部分信息

- Controller/DRAM 配置对布线规则的影响

- HyperLynx 布线后验证助力设计优化

内容花絮:

- DDR 接口的正常工作,要求满足不同信号组之间的信号完整性和时序要求。为了减少改版次数,在PCB制造之前,通过验证从而确保设计满足所有要求。传统上,设计师依靠信号完整性专家来进行仿真验证工作,完全芯片厂商提供的PCB设计指导,不进行任何仿真验证工作,希望能够通过物理原型测试发现设计缺陷。不断升高的速率,DDR接口的工作余量越来越小,简单的遵循物理设计规则已经不能满足设计要求。

- 本次电巢直播将分享DDR设计中电气规则的特殊性,快速进行布线后仿真验证。

适合对象:

- 在校学生

- 来串门的同行

- 想学习的人群

- 有超车涨薪需求的人群

- 对仿真感兴趣的电子工程师

- 对HyperLynx感兴趣的电子工程师

目录

{

"id": "181",

"isDefault": "1",

"learnMode": "freeMode",

"isMember": "",

"status": "published",

"currentTaskId": "",

"isHideUnpublish": "0"

}

{

"i18nChapterName": "章",

"i18nUnitName": "节",

"i18nLessonName": "课时",

"i18nTaskName":"任务"

}

[{"itemType":"chapter","number":"1","published_number":0,"title":"\u8bfe\u7a0b\u76ee\u6807\u53caDDR4\u8bbe\u8ba1\u6982\u8ff0","result":"","resultStatus":"","lock":"","status":"published","taskId":"2693","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"1","published_number":"1","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u8bfe\u7a0b\u76ee\u6807\u53caDDR4\u8bbe\u8ba1\u6982\u8ff0","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2496","isOptional":"0","type":"video","isTaskFree":"1","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"06:33","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"2","published_number":0,"title":"DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u7efc\u8ff0\uff09","result":"","resultStatus":"","lock":"","status":"published","taskId":"2695","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"2","published_number":"2","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\u7efc\u8ff0","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2497","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"08:10","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"3","published_number":0,"title":"DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e0a\uff09","result":"","resultStatus":"","lock":"","status":"published","taskId":"2697","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"3","published_number":"3","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e0a\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2498","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"10:28","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"4","published_number":0,"title":"DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e2d\uff09","result":"","resultStatus":"","lock":"","status":"published","taskId":"2699","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"4","published_number":"4","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e2d\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2499","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"11:31","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"5","published_number":0,"title":"DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e0b\uff09","result":"","resultStatus":"","lock":"","status":"published","taskId":"2701","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"5","published_number":"5","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e0b\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2500","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"07:24","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"6","published_number":0,"title":"DDRx\u540e\u4eff\u771f\u6d41\u7a0b","result":"","resultStatus":"","lock":"","status":"published","taskId":"2703","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"6","published_number":"6","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDRx\u540e\u4eff\u771f\u6d41\u7a0b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2501","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"05:23","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"7","published_number":0,"title":"DDR4\u540e\u4eff\u771f\u6f14\u793a","result":"","resultStatus":"","lock":"","status":"published","taskId":"2704","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"7","published_number":"7","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011Memory-down ddr\u63a5\u53e3\u6f14\u793a","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2502","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"12:27","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"8","published_number":"8","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u30111-Model-free","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2503","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"9","published_number":"9","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u30112-Models-Xilinx","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2504","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"10","published_number":"10","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u30113-\u9644\u52a0\u901a\u7528\u6a21\u578b\u811a\u672c-assign_GenericIBIS","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2505","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"11","published_number":"11","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u52a0\u8f7d\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2506","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:42","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"12","published_number":"12","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u68c0\u67e5\u8bbe\u7f6e","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2507","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:24","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"13","published_number":"13","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u8fd0\u884c\u4ea4\u4e92\u626b\u63cf","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2508","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"02:28","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"14","published_number":"14","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u4f7f\u7528Ref File\u9644IBIS\u6a21\u578b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2509","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:39","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"15","published_number":"15","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u901a\u7528\u6279\u5904\u7406\u4e32\u6270\u4eff\u771f","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2510","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"04:03","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"16","published_number":"16","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u8fd0\u884cDDRx\u5411\u5bfc","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2511","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"03:51","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"17","published_number":"17","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u67e5\u770bDDRx Wizard \u62a5\u544a","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2512","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"06:19","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"18","published_number":"18","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2513","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"19","published_number":"19","title":"\u3010\u8bfe\u4ef6\u3011DDRx\u4eff\u771f\u5b9e\u8df5 \u7b2c\u4e09\u671f\uff1a\u8d85\u8f66\u7bc7_\u5f2f\u90532-DDRx\u540e\u4eff\u771f\u5b9e\u8df5","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2772","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true}]

{

"text": {

"icon": "es-icon es-icon-graphicclass",

"name": "图文"

}

,

"video": {

"icon": "es-icon es-icon-videoclass",

"name": "视频"

}

,

"audio": {

"icon": "es-icon es-icon-audioclass",

"name": "音频"

}

,

"live": {

"icon": "es-icon es-icon-videocam",

"name": "直播"

}

,

"discuss": {

"icon": "es-icon es-icon-comment",

"name": "讨论"

}

,

"flash": {

"icon": "es-icon es-icon-flashclass",

"name": "Flash"

}

,

"doc": {

"icon": "es-icon es-icon-description",

"name": "文档"

}

,

"ppt": {

"icon": "es-icon es-icon-pptclass",

"name": "PPT"

}

,

"testpaper": {

"icon": "es-icon es-icon-kaoshi",

"name": "考试"

}

,

"homework": {

"icon": "es-icon es-icon-zuoye",

"name": "作业"

}

,

"exercise": {

"icon": "es-icon es-icon-mylibrarybooks",

"name": "练习"

}

,

"download": {

"icon": "es-icon es-icon-filedownload",

"name": "下载资料"

}

}

1732238295

授课教师

PCB设计专家

课程特色

视频(14)

下载资料(5)

学员动态

lxcxab

开始学习 【随堂演示】检查设置

zzz777

开始学习 【随堂演示】查看DDRx Wi...

zzz777

完成了 【随堂演示】运行DDRx向导

zzz777

开始学习 【随堂演示】运行DDRx向导