课程介绍

讲师介绍:

胡建伟

- 亚太区Mentor EDA分销部门应用工程师经理

- Mentor PCB仿真分析产品技术支持

- EDA行业从业并管理20+年

胡建伟于1999年毕业于东南大学,并获得数字信号处理硕士学位。在高速PCB设计领域拥有丰富的经验和背景,曾任Cadence高级应用工程师,负责支持Cadence PCB设计及仿真工具。

彭水飞

- 原中兴通讯互连设计专家

- EDA365 Mentor 论坛特邀版主

- 10多年通讯设备PCB设计经验

彭水飞在高速、高密度、数模混合电路等多类型PCB设计方面具备丰富的实战经验。在互连设计领域相关质量建设、效率提升及流程优化方面能力突出。

2010年获得Mentor全球计算机PCB设计大赛金奖

2016年获得IPC中国区PCB设计大赛冠军

直播介绍:

当今电子产品一个很重要的区分元素是其所用的存储器。服务器、计算机、智能手机、游戏机、GPS 以及几乎所有类似产品使用的都是现代处理器和 FPGA。这些设备需要高速、高带宽、双倍数据速率 (DDR)存储器才能运行。每一代 DDR SDRAM(双倍数据速率同步动态随机存取存储器)都会带来新的优势,例如速度和容量的提升以及功耗的下降。要满足速度提升,功耗降低的要求,就要应对设计余量降低的挑战。

如何应对挑战不重要,重要的是我们要超车,那就跟着我们学DDRx的仿真!

课程特色:

- 我做:介绍知识背景和我们的练习案例

- 我们一起做:一两个练习,

- 你们课后做:研究其他的练习

课程要点:

- 超车计划:超车涨薪仿真训练营全貌预览

- 阅历分享:仿真老司机谈自己仿真江湖事

- 一起上车:带你建立仿真知识图谱,简单快速学仿真基础知识

- 设计叠层以满足阻抗要求

- 平衡阻抗与串扰的不同组内间距要求

- 基于串扰要求,平衡驱动力和组内间距的要求

- 通过仿真分析获取板级设计规则

- 在PCB设计之前预计设计余量

- 优化驱动力和ODT设置

- DDR接口的信号完整性和时序电气规则

- “遵循设计指导布线”为何不再完美

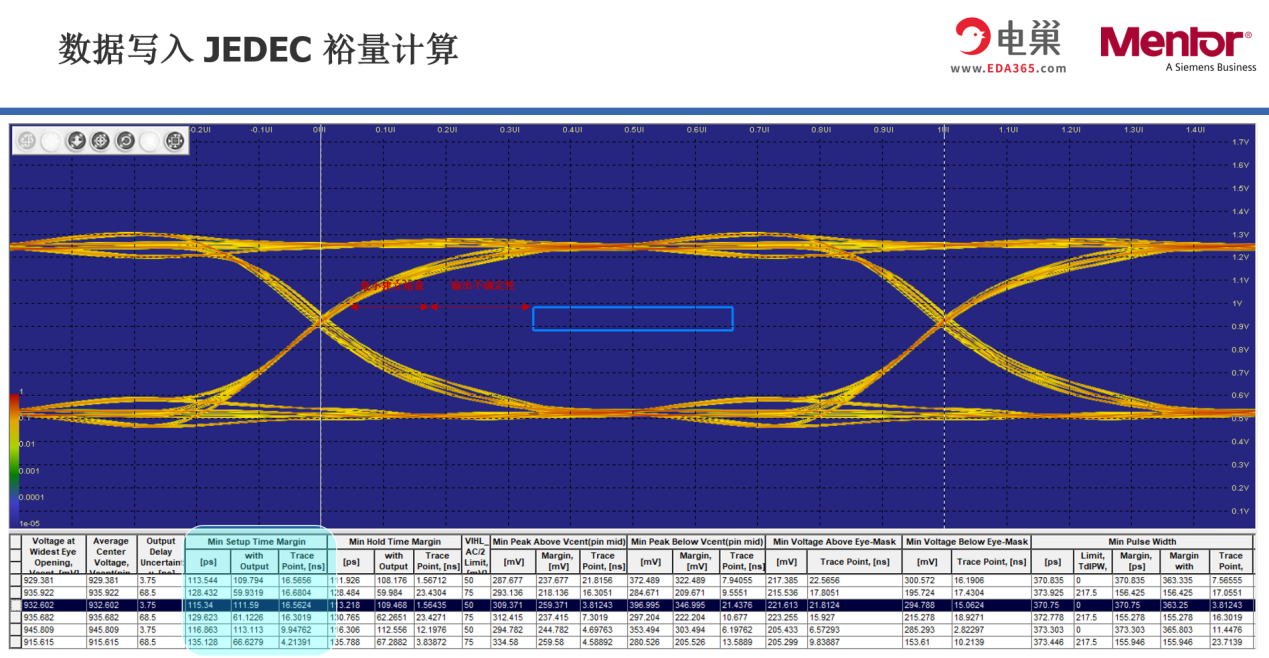

- 为什么JEDEC 规范只能提供验证所需的部分信息

- Controller/DRAM 配置对布线规则的影响

- HyperLynx 布线后验证助力设计优化

- PCB板上PDN噪声来源

- 信号完整性与PDN协同仿真框架

- HyperLynx 信号完整性与PDN噪声协同验证方案

- HyperLynx DDR4 PowerAware 仿真演示

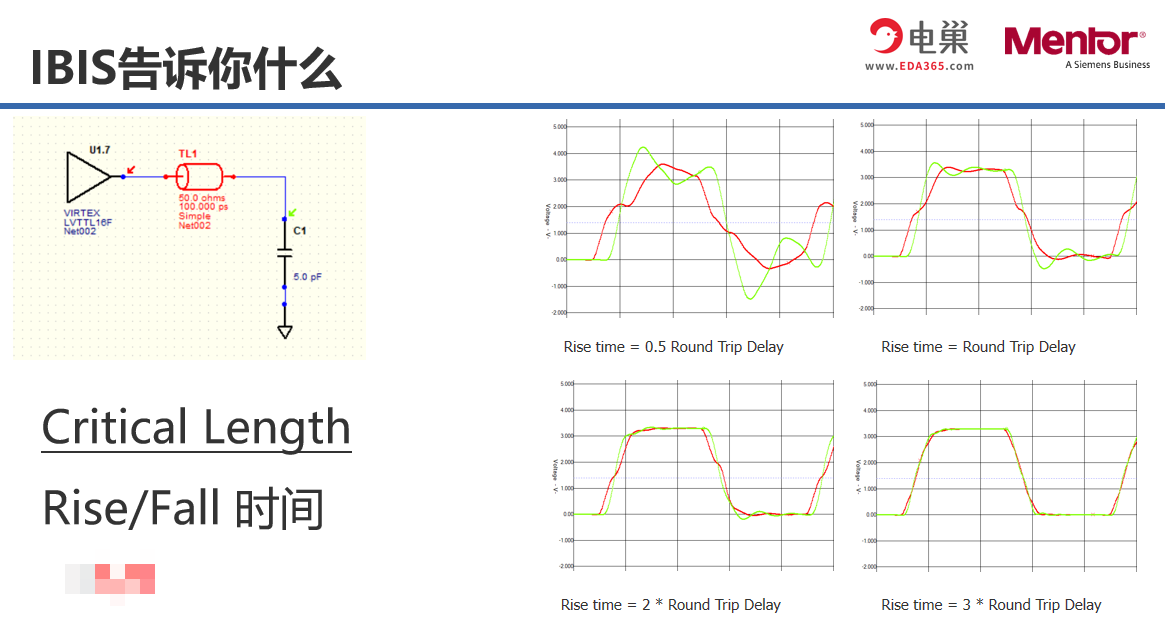

- IBIS 模型概述

- IBIS能告诉你什么

- 被动元件IBIS建模

- FPGA芯片IBIS建模

- Spice模型的IBIS引用

内容花絮:

适合对象:

- 在校学生

- 来串门的同行

- 想学习的人群

- 有超车涨薪需求的人群

- 对仿真感兴趣的电子工程师

- 对HyperLynx感兴趣的电子工程师

目录

{

"id": "206",

"isDefault": "1",

"learnMode": "freeMode",

"isMember": "",

"status": "published",

"currentTaskId": "",

"isHideUnpublish": "0"

}

{

"i18nChapterName": "章",

"i18nUnitName": "节",

"i18nLessonName": "课时",

"i18nTaskName":"任务"

}

[{"itemType":"chapter","number":"1","published_number":0,"title":"\u914d\u7f6e\u7bc7-\u5982\u4f55\u5728\u4eff\u771f\u8d5b\u9053\u4e0a\u9a70\u9a8b\uff1f","result":"","resultStatus":"","lock":"","status":"published","taskId":"2992","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"unit","number":"1","published_number":0,"title":"\u8bfe\u7a0b\u4ecb\u7ecd","result":"","resultStatus":"","lock":"","status":"published","taskId":"2993","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"1","published_number":"1","title":"Mentor\u9ad8\u7ba1\u5bc4\u8bed","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2777","isOptional":"0","type":"video","isTaskFree":"1","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"12:55","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"2","published_number":"2","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u8d85\u8f66\u8ba1\u5212\u4ecb\u7ecd---\u5f6d\u6c34\u98de\u8001\u5e08","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2778","isOptional":"0","type":"video","isTaskFree":"1","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"23:54","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"3","published_number":"3","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u4eff\u771f\u6240\u9700\u8981\u5efa\u7acb\u7684\u77e5\u8bc6\u80cc\u666f---\u80e1\u5efa\u4f1f\u8001\u5e08","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2779","isOptional":"0","type":"video","isTaskFree":"1","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"09:13","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"4","published_number":"4","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u3011Models","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2780","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"2","published_number":0,"title":"\u963b\u6297\u4e0e\u53e0\u5c42","result":"","resultStatus":"","lock":"","status":"published","taskId":"2998","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"5","published_number":"5","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u963b\u6297\u4e0e\u53e0\u5c42","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2781","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"07:00","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"6","published_number":"6","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module1_Lab1&Lab2_\u63a2\u8ba8\u51e0\u4f55\u622a\u9762\u5982\u4f55\u5f71\u54cd\u5fae\u5e26\u7ebf\u548c\u5e26\u72b6\u7ebf\u7684Z0\u548cTD","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2782","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"03:16","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"7","published_number":"7","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module1_Lab3_\u4f7f\u7528\u53e0\u5c42\u7f16\u8f91\u5668\u6765\u8bbe\u8ba1\u4f20\u8f93\u7ebf","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2783","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"02:31","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"8","published_number":"8","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u8ba4\u8bc6\u53e0\u5c42\u7f16\u8f91\u5668","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2784","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"10:08","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"9","published_number":"9","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011\u963b\u6297\u548c\u53e0\u5c42","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2785","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"3","published_number":0,"title":"\u53cd\u5c04\u4e0e\u7ec8\u7aef\u5339\u914d","result":"","resultStatus":"","lock":"","status":"published","taskId":"3004","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"10","published_number":"10","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u53cd\u5c04\u4e0e\u7ec8\u7aef\u5339\u914d","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2786","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"16:25","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"11","published_number":"11","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module2_Lab1_\u6ca1\u6709\u7aef\u63a5\u7684\u53cd\u5c04\u566a\u58f0\u548c\u566a\u58f0\u5bb9\u9650","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2787","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"08:45","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"12","published_number":"12","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011\u53cd\u5c04\u4e0e\u7ec8\u7aef\u5339\u914d.7z","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2788","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"4","published_number":0,"title":"\u4e32\u6270","result":"","resultStatus":"","lock":"","status":"published","taskId":"3008","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"13","published_number":"13","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u4e32\u6270","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2789","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"08:22","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"14","published_number":"14","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module3_Lab1_\u521b\u5efa\u8026\u5408\u7ebf\u548c\u7535\u78c1\u573a\u7ebf","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2790","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:30","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"15","published_number":"15","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module3_Lab9_\u6709\u6548\u7684\u4fdd\u62a4\u7ebf","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2791","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"05:05","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"16","published_number":"16","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011\u4e32\u6270.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2792","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"5","published_number":0,"title":"\u5dee\u5206\u5bf9","result":"","resultStatus":"","lock":"","status":"published","taskId":"3013","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"17","published_number":"17","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u5dee\u5206\u5bf9","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2793","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"07:15","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"18","published_number":"18","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module4_Lab1_\u5dee\u5206\u548c\u5355\u7aef\u4fe1\u53f7","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2794","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"04:33","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"19","published_number":"19","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module4_Lab5_\u4e0d\u6070\u5f53\u7684\u5dee\u5206\u7aef\u63a5\u9020\u6210\u7684\u5f71\u54cd","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2795","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"03:24","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"20","published_number":"20","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011\u5dee\u5206\u5bf9.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2796","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"6","published_number":0,"title":"\u635f\u8017\u548c\u9ad8\u901f\u4e32\u884c\u901a\u9053","result":"","resultStatus":"","lock":"","status":"published","taskId":"3018","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"21","published_number":"21","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u635f\u8017\u4e0e\u9ad8\u901f\u4e32\u884c\u901a\u9053","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2797","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"12:31","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"22","published_number":"22","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module5_Lab3_\u8f93\u51fa s21\u548c sdd21\u8bc4\u4f30\u8bbe\u8ba1\u635f\u8017","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2798","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:27","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"23","published_number":"23","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module5_Lab4_\u6700\u9ad8\u7684\u6570\u636e\u901f\u7387\u548c\u4fe1\u9053\u8870\u51cf@the nyquist","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2799","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"02:09","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"24","published_number":"24","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011\u635f\u8017\u548c\u9ad8\u901f\u4e32\u884c\u901a\u9053.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2800","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"7","published_number":0,"title":"\u4f9b\u7535\u7f51\u7edc","result":"","resultStatus":"","lock":"","status":"published","taskId":"3023","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"25","published_number":"25","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u4f9b\u7535\u7f51\u7edc","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2801","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"17:00","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"26","published_number":"26","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module6_Lab1_\u5e73\u9762\u963b\u6297\u7684\u4eff\u771f","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2802","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"04:15","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"27","published_number":"27","title":"\u3010\u968f\u5802\u6f14\u793a\u3011Module6_Lab2_\u589e\u52a0\u7535\u538b\u8c03\u6574\u6a21\u5757\u63a2\u8ba8\u5bf9\u5e73\u9762\u963b\u6297\u7684\u5f71\u54cd","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2803","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:44","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"8","published_number":0,"title":"\u672c\u7ae0\u8bfe\u4ef6","result":"","resultStatus":"","lock":"","status":"published","taskId":"3119","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"28","published_number":"28","title":"\u3010\u8bfe\u4ef6\u3011\u914d\u7f6e\u7bc7-\u5982\u4f55\u5728\u4eff\u771f\u8d5b\u9053\u4e0a\u9a70\u9a8b\uff1f","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2868","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"2","published_number":0,"title":"\u8d85\u8f66\u7bc7_\u5f2f\u90531-DDRx\u524d\u4eff\u771f\u5b9e\u8df5","result":"","resultStatus":"","lock":"","status":"published","taskId":"3027","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"unit","number":"1","published_number":0,"title":"\u77e5\u8bc6\u80cc\u666f","result":"","resultStatus":"","lock":"","status":"published","taskId":"3028","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"29","published_number":"29","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u5e03\u7ebf\u524d\u4eff\u771f\u7684\u91cd\u8981\u6027\u53caDDRx \u8bbe\u8ba1\u6d41\u7a0b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2804","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"05:21","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"30","published_number":"30","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4 \u8bbe\u8ba1\u4e2d\u9700\u8981\u5173\u6ce8\u7684\u7535\u6c14\u56e0\u7d20\uff08\u4e0a\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2805","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"09:32","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"31","published_number":"31","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4 \u8bbe\u8ba1\u4e2d\u9700\u8981\u5173\u6ce8\u7684\u7535\u6c14\u56e0\u7d20\uff08\u4e0b\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2806","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"11:48","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"32","published_number":"32","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u3011models.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2807","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"2","published_number":0,"title":"\u53e0\u5c42\u8bbe\u8ba1","result":"","resultStatus":"","lock":"","status":"published","taskId":"3033","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"33","published_number":"33","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u53e0\u5c42\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2808","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"06:04","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"34","published_number":"34","title":"\u3010\u968f\u5802\u6f14\u793a\u3011HL\u4e2d\u53e0\u5c42&\u963b\u6297&\u710a\u76d8\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2809","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"04:14","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"35","published_number":"35","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011DQ_DQS_THVia.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2810","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"3","published_number":0,"title":"\u8fc7\u5b54\u8bbe\u8ba1","result":"","resultStatus":"","lock":"","status":"published","taskId":"3037","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"36","published_number":"36","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u8fc7\u5b54\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2811","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"09:23","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"37","published_number":"37","title":"\u3010\u968f\u5802\u6f14\u793a\u3011HL\u4e2d\u8fc7\u5b54\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2812","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"04:08","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"38","published_number":"38","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011Via_Design.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2813","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"4","published_number":0,"title":"ACC CK \u603b\u7ebf\u8bbe\u8ba1","result":"","resultStatus":"","lock":"","status":"published","taskId":"3042","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"39","published_number":"39","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011ACC CK \u603b\u7ebf\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2815","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"15:03","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"40","published_number":"40","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u5730\u5740\u5206\u652f\u957f\u5ea6\u626b\u63cf\u5206\u6790","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2816","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"03:31","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"41","published_number":"41","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u5730\u5740\u5206\u652f\u957f\u5ea6\u4eff\u771f\u62a5\u544a","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2817","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"03:41","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"42","published_number":"42","title":"\u3010\u8054\u7cfb\u6587\u4ef6\u3011Address_Clk_THVia.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2818","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"5","published_number":0,"title":"DQ DQS \u603b\u7ebf\u8bbe\u8ba1","result":"","resultStatus":"","lock":"","status":"published","taskId":"3048","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"43","published_number":"43","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DQ DQS \u603b\u7ebf\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2819","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"13:58","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"44","published_number":"44","title":"\u3010\u968f\u5802\u6f14\u793a\u3011DQ\u957f\u5ea6\u626b\u63cf\u5206\u6790","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2820","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"03:06","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"45","published_number":"45","title":"\u3010\u968f\u5802\u6f14\u793a\u3011DQ\u957f\u5ea6\u626b\u63cf\u4eff\u771f\u62a5\u544a\u67e5\u770b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2821","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:42","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"46","published_number":"46","title":"\u3010\u968f\u5802\u6f14\u793a\u3011ODT\u626b\u63cf\u5206\u6790","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2822","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"05:46","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"47","published_number":"47","title":"\u3010\u968f\u5802\u6f14\u793a\u3011ODT\u626b\u63cf\u62a5\u544a\u67e5\u770b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2823","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"05:49","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"48","published_number":"48","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011DQ_DQS_THVia.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2824","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"6","published_number":0,"title":"\u5e03\u7ebf\u524d\u4eff\u771f\u6f14\u793a","result":"","resultStatus":"","lock":"","status":"published","taskId":"3055","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"49","published_number":"49","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u5e03\u7ebf\u524d\u4eff\u771f\u6f14\u793a","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2825","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"09:07","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"7","published_number":0,"title":"\u672c\u7ae0\u8bfe\u4ef6","result":"","resultStatus":"","lock":"","status":"published","taskId":"3121","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"50","published_number":"50","title":"\u3010\u8bfe\u4ef6\u3011\u8d85\u8f66\u7bc7_\u5f2f\u90531-DDRx\u524d\u4eff\u771f\u5b9e\u8df5","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2869","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"3","published_number":0,"title":"\u8d85\u8f66\u7bc7_\u5f2f\u90532-DDRx\u540e\u4eff\u771f\u5b9e\u8df5","result":"","resultStatus":"","lock":"","status":"published","taskId":"3057","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"unit","number":"1","published_number":0,"title":"\u8bfe\u7a0b\u76ee\u6807\u53caDDR4\u8bbe\u8ba1\u6982\u8ff0","result":"","resultStatus":"","lock":"","status":"published","taskId":"3058","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"51","published_number":"51","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u8bfe\u7a0b\u76ee\u6807\u53caDDR4\u8bbe\u8ba1\u6982\u8ff0","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2826","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"06:33","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"2","published_number":0,"title":"DDR4\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\u7efc\u8ff0","result":"","resultStatus":"","lock":"","status":"published","taskId":"3060","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"52","published_number":"52","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\u7efc\u8ff0","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2827","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"08:10","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"3","published_number":0,"title":"DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e0a\uff09","result":"","resultStatus":"","lock":"","status":"published","taskId":"3062","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"53","published_number":"53","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e0a\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2828","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"10:28","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"4","published_number":0,"title":"DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e2d\uff09","result":"","resultStatus":"","lock":"","status":"published","taskId":"3064","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"54","published_number":"54","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e2d\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2829","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"11:31","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"5","published_number":0,"title":"DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e0b\uff09","result":"","resultStatus":"","lock":"","status":"published","taskId":"3066","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"55","published_number":"55","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDR4\u4eff\u771f\u8bbe\u8ba1\u7535\u6c14\u56e0\u7d20\uff08\u4e0b\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2830","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"07:24","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"6","published_number":0,"title":"DDRx\u540e\u4eff\u771f\u6d41\u7a0b","result":"","resultStatus":"","lock":"","status":"published","taskId":"3068","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"56","published_number":"56","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011DDRx\u540e\u4eff\u771f\u6d41\u7a0b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2831","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"05:23","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"7","published_number":0,"title":"DDR4\u540e\u4eff\u771f\u6f14\u793a","result":"","resultStatus":"","lock":"","status":"published","taskId":"3070","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"57","published_number":"57","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011Memory-down ddr\u63a5\u53e3\u6f14\u793a","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2832","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"12:27","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"58","published_number":"58","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u30111-Model-free.7z","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2833","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"59","published_number":"59","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u30112-Models-Xilinx.7z","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2834","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"60","published_number":"60","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u30113-\u9644\u52a0\u901a\u7528\u6a21\u578b\u811a\u672c-assign_GenericIBIS.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2835","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"61","published_number":"61","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u52a0\u8f7d\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2836","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:42","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"62","published_number":"62","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u68c0\u67e5\u8bbe\u7f6e","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2837","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:24","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"63","published_number":"63","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u8fd0\u884c\u4ea4\u4e92\u626b\u63cf","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2838","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"02:28","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"64","published_number":"64","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u4f7f\u7528Ref File\u9644IBIS\u6a21\u578b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2839","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:39","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"65","published_number":"65","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u901a\u7528\u6279\u5904\u7406\u4e32\u6270\u4eff\u771f","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2840","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"04:03","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"66","published_number":"66","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u8fd0\u884cDDRx\u5411\u5bfc","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2841","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"03:51","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"67","published_number":"67","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u67e5\u770bDDRx Wizard \u62a5\u544a","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2842","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"06:19","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"68","published_number":"68","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011dBRICK.rar","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2843","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"8","published_number":0,"title":"\u672c\u7ae0\u8bfe\u4ef6","result":"","resultStatus":"","lock":"","status":"published","taskId":"3123","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"69","published_number":"69","title":"\u3010\u8bfe\u4ef6\u3011\u8d85\u8f66\u7bc7_\u5f2f\u90532-DDRx\u540e\u4eff\u771f\u5b9e\u8df5","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2870","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"4","published_number":0,"title":"\u8d85\u8f66\u7bc7_\u5f2f\u90533-DDR4 SI\/PI \u534f\u540c\u4eff\u771f","result":"","resultStatus":"","lock":"","status":"published","taskId":"3083","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"unit","number":"1","published_number":0,"title":"PCB\u677f\u4e0aPDN\u566a\u58f0\u6765\u6e90","result":"","resultStatus":"","lock":"","status":"published","taskId":"3084","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"70","published_number":"70","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011PCB\u677f\u4e0aPDN\u566a\u58f0\u6765\u6e90","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2844","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"08:53","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"2","published_number":0,"title":"\u4fe1\u53f7\u5b8c\u6574\u6027\u4e0ePDN\u534f\u540c\u4eff\u771f\u6846\u67b6","result":"","resultStatus":"","lock":"","status":"published","taskId":"3086","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"71","published_number":"71","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u4fe1\u53f7\u5b8c\u6574\u6027\u4e0ePDN\u534f\u540c\u4eff\u771f\u6846\u67b6","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2845","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"16:18","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"3","published_number":0,"title":"\u4fe1\u53f7\u5b8c\u6574\u6027\u4e0ePDN\u566a\u58f0\u534f\u540c\u9a8c\u8bc1\u65b9\u6848","result":"","resultStatus":"","lock":"","status":"published","taskId":"3088","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"72","published_number":"72","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011HyperLynx \u4fe1\u53f7\u5b8c\u6574\u6027\u4e0ePDN\u566a\u58f0\u534f\u540c\u9a8c\u8bc1\u65b9\u6848","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2846","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"14:50","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"4","published_number":0,"title":"HyperLynx DDR4 Power-Aware \u4eff\u771f\u6f14\u793a","result":"","resultStatus":"","lock":"","status":"published","taskId":"3090","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"73","published_number":"73","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011HyperLynx DDR4 PowerAware \u4eff\u771f\u6f14\u793a\uff08\u4e0a\uff09","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2847","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"10:01","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"74","published_number":"74","title":" \u3010\u76f4\u64ad\u8bb2\u89e3\u3011HyperLynx DDR4 PowerAware \u4eff\u771f\u6f14\u793a\uff08\u4e0b\uff09&\u76f4\u64ad\u603b\u7ed3","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2848","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"12:35","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"5","published_number":0,"title":"Power-Aware\u4eff\u771f\u968f\u5802\u6f14\u793a","result":"","resultStatus":"","lock":"","status":"published","taskId":"3093","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"75","published_number":"75","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u67e5\u770bDRAM POWER AWARE IBIS\u6a21\u578b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2849","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:07","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"76","published_number":"76","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u8bbe\u7f6e\u5de5\u5177\u9009\u9879","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2850","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"00:50","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"77","published_number":"77","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u719f\u6089\u8bbe\u8ba1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2851","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"02:41","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"78","published_number":"78","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u68c0\u67e5\u8bbe\u8ba1\u8bbe\u7f6e","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2852","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:29","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"79","published_number":"79","title":"\u3010\u968f\u5802\u6f14\u793a\u3011PDN&Channel\u63d0\u53d6\u4ecb\u7ecd","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2853","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:39","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"80","published_number":"80","title":" \u3010\u968f\u5802\u6f14\u793a\u3011\u63d0\u53d6Data Byte Lane 0 and 1V2","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2854","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"03:19","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"81","published_number":"81","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u4eff\u771f\u524d\u51c6\u5907","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2855","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:30","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"82","published_number":"82","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u566a\u58f0\u5bf9\u6bd4\uff1a\u7406\u60f3\u4e0e\u975e\u7406\u60f3PDN","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2856","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"02:23","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"83","published_number":"83","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u89c2\u5bdf1.2V\u7684SSN","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2857","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:24","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"84","published_number":"84","title":" \u3010\u968f\u5802\u6f14\u793a\u3011\u773c\u56fe\u5bf9\u6bd4\uff1a\u7406\u60f3\u4e0e\u975e\u7406\u60f3SSN","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2858","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"02:27","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"85","published_number":"85","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u4f7f\u7528\u7406\u60f3PDN\u8fd0\u884cDDRx\u5411\u5bfc","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2859","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"01:44","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"86","published_number":"86","title":"\u3010\u968f\u5802\u6f14\u793a\u3011\u4f7f\u7528\u975e\u7406\u60f3PDN\u8fd0\u884cDDRx\u5411\u5bfc","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2860","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"02:09","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"87","published_number":"87","title":"\u3010\u8bfe\u7a0b\u6a21\u578b\u3011models.7z","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2861","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"88","published_number":"88","title":"\u3010\u7ec3\u4e60\u6587\u4ef6\u3011DDR4_PowerAware_Workshop_VX.2.6.zip","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2862","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"6","published_number":0,"title":"\u672c\u7ae0\u8bfe\u4ef6","result":"","resultStatus":"","lock":"","status":"published","taskId":"3125","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"89","published_number":"89","title":"\u3010\u8bfe\u4ef6\u3011\u8d85\u8f66\u7bc7_\u5f2f\u90533-DDR4 SIPI \u534f\u540c\u4eff\u771f","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2871","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"5","published_number":0,"title":"\u8d85\u8f66\u7bc7_\u6a21\u578b\u64cd\u76d8\u624b-IBIS\u5efa\u6a21\u4e0e\u5e94\u7528\u5b9e\u6218","result":"","resultStatus":"","lock":"","status":"published","taskId":"3108","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"unit","number":"1","published_number":0,"title":"IBIS \u6a21\u578b\u6982\u8ff0","result":"","resultStatus":"","lock":"","status":"published","taskId":"3109","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"90","published_number":"90","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011IBIS \u6a21\u578b\u6982\u8ff0","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2863","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"10:28","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"2","published_number":0,"title":"IBIS\u544a\u8bc9\u4f60\u4ec0\u4e48","result":"","resultStatus":"","lock":"","status":"published","taskId":"3111","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"91","published_number":"91","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011IBIS\u544a\u8bc9\u4f60\u4ec0\u4e48","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2864","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"26:14","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"3","published_number":0,"title":"\u88ab\u52a8\u5143\u4ef6\u53caFPGA\u82af\u7247 IBIS\u5efa\u6a21","result":"","resultStatus":"","lock":"","status":"published","taskId":"3113","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"92","published_number":"92","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u88ab\u52a8\u5143\u4ef6\u53caFPGA\u82af\u7247 IBIS\u5efa\u6a21","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2865","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"08:59","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"4","published_number":0,"title":"Spice\u6a21\u578b\u7684IBIS\u5f15\u7528","result":"","resultStatus":"","lock":"","status":"published","taskId":"3115","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"93","published_number":"93","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011Spice\u6a21\u578b\u7684IBIS\u5f15\u7528","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2866","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"10:50","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"5","published_number":0,"title":"\u8bfe\u7a0b\u5c0f\u7ed3","result":"","resultStatus":"","lock":"","status":"published","taskId":"3117","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"94","published_number":"94","title":"\u3010\u76f4\u64ad\u8bb2\u89e3\u3011\u8bfe\u7a0b\u5c0f\u7ed3","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2867","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"04:43","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"unit","number":"6","published_number":0,"title":"\u672c\u7ae0\u8bfe\u4ef6","result":"","resultStatus":"","lock":"","status":"published","taskId":"3127","isOptional":"0","type":"unit","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"95","published_number":"95","title":"\u3010\u8bfe\u4ef6\u3011\u8d85\u8f66\u7bc7_\u6a21\u578b\u64cd\u76d8\u624b-IBIS\u5efa\u6a21\u4e0e\u5e94\u7528\u5b9e\u6218","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2872","isOptional":"0","type":"download","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"chapter","number":"6","published_number":0,"title":"\u7535\u5b50\u5de5\u7a0b\u5e08\u8d85\u8f66\u8ba1\u5212\u4e4bDDRx\u4eff\u771f\u5b9e\u8df5\u4e4b\u603b\u7ed3\u7bc7\uff1a\u4e13\u5bb6\u7b54\u7591\u4e13\u573a","result":"","resultStatus":"","lock":"","status":"published","taskId":"3139","isOptional":"0","type":"chapter","isTaskFree":"","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"","activityEndTime":"","fileStorage":"","isTaskTryLookable":"","isSingleTaskLesson":false},{"itemType":"task","number":"96","published_number":"96","title":"\u8d85\u8f66\u8ba1\u5212\u603b\u4f53\u56de\u987e1","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2883","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"15:04","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"97","published_number":"97","title":"\u8d85\u8f66\u8ba1\u5212\u603b\u4f53\u56de\u987e2","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2884","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"12:21","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"98","published_number":"98","title":"\u8d85\u8f66\u8ba1\u5212\u7b54\u75911","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2885","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"17:42","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"99","published_number":"99","title":"\u8d85\u8f66\u8ba1\u5212\u7b54\u75912","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2886","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"12:08","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true},{"itemType":"task","number":"100","published_number":"100","title":"\u8bfe\u7a0b\u5c55\u671b","result":"","resultStatus":"","lock":false,"status":"published","taskId":"2887","isOptional":"0","type":"video","isTaskFree":"0","watchLimitRemaining":false,"replayStatus":"","activityStartTimeStr":"","activityStartTime":"","activityLength":"14:42","activityEndTime":"","fileStorage":"local","isTaskTryLookable":0,"isSingleTaskLesson":true}]

{

"text": {

"icon": "es-icon es-icon-graphicclass",

"name": "图文"

}

,

"video": {

"icon": "es-icon es-icon-videoclass",

"name": "视频"

}

,

"audio": {

"icon": "es-icon es-icon-audioclass",

"name": "音频"

}

,

"live": {

"icon": "es-icon es-icon-videocam",

"name": "直播"

}

,

"discuss": {

"icon": "es-icon es-icon-comment",

"name": "讨论"

}

,

"flash": {

"icon": "es-icon es-icon-flashclass",

"name": "Flash"

}

,

"doc": {

"icon": "es-icon es-icon-description",

"name": "文档"

}

,

"ppt": {

"icon": "es-icon es-icon-pptclass",

"name": "PPT"

}

,

"testpaper": {

"icon": "es-icon es-icon-kaoshi",

"name": "考试"

}

,

"homework": {

"icon": "es-icon es-icon-zuoye",

"name": "作业"

}

,

"exercise": {

"icon": "es-icon es-icon-mylibrarybooks",

"name": "练习"

}

,

"download": {

"icon": "es-icon es-icon-filedownload",

"name": "下载资料"

}

}

1732184965

授课教师

PCB设计专家

课程特色

视频(78)

下载资料(22)