课程介绍

感谢您使用电巢APP, PC端建议使用Google Chrome浏览器进行观看!

讲师介绍:

荣庆安老师|EDA365论坛特邀版主,原华为器件可靠性技术首席专家

- 原华为器件可靠性技术首席专家、器件工程专家组主任、器件归一化工作奠基人;

- 20多年交换机、路由器、传输、基站等产品器件工程设计;

- 主持多项重大失效问题攻关,完成了逻辑、储存、光器件等领域器件优选库建设;

- 参与中国器件标准工作,国内外发表论文4篇,获器件相关6项发明专利。

孙雅琪

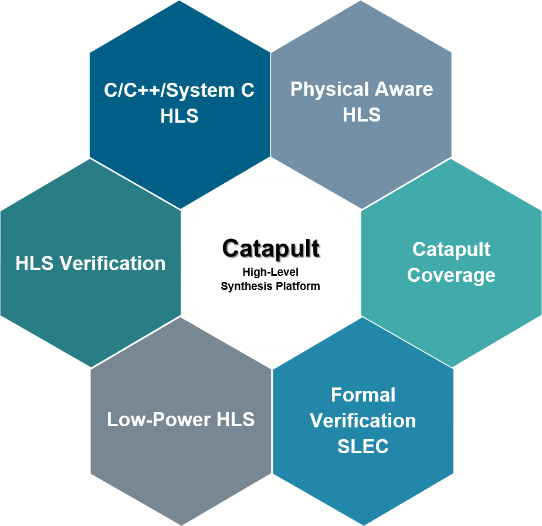

- 在 Siemens Digital Industries Software 担任 Catapult 高层次综合平台的 HLS 应用工程师。

- 专注领域包括 FPGA、DSP 以及机器学习硬件设计。

- 获得了南京航空航天大学电气科学与技术学士学位,以及美国德州农工大学的电气工程硕士学位。

课程介绍:

- 高层次综合(High-Level Synthesis, HLS)扩展了传统的设计流程,允许工程师在更高抽象层级进行硬件设计与验证,为硬件设计提供了一种新的、强大的方法。本次研讨会第一部分将首先介绍HLS的基本概念、工作流程与设计方法, 并解释使用HLS方法学所带来的优势。。

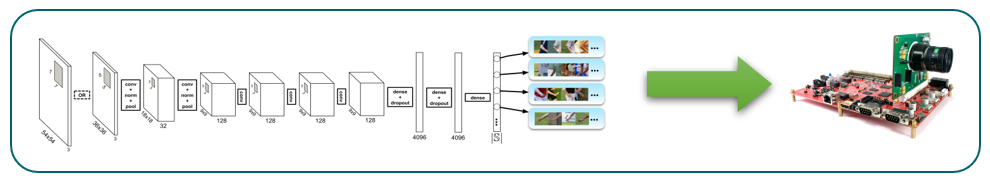

- 本次研讨会的第二部分我们将使用一个AI算法——tinyYOLO为例,展示围绕Catapult建立的HLS设计和验证流程及其相关工作系统,与传统的基于RTL的流程相比,如何显著加快AI / ML硬件加速器的设计。它将着重使用NVIDIA的开源MatchLib SystemC库执行ML加速器的快速建模与综合。我们将演示使用MatchLib进行的仿真如何识别和修复潜在的系统级性能问题,而这些问题通常在手工编码的RTL设计中很晚才会被发现。

- 最后我们将演示如何使用Catapult HLS工具进行此AI算法的硬件实现并最终在FPGA板上运行该设计。