课程介绍

感谢您使用电巢APP,PC端建议使用Google Chrome浏览器进行观看!

讲师介绍:

杨善明老师:EDA365论坛特邀版主,原华为工艺技术专家

- 杨老师从事产品硬件工程工艺研发、技术管理10多年,完成过接入网,承载网,OTN产品的开发,从产品的设计到试制到量产,实现全流程端到端的解决问题,有丰富的产品问题攻关及技术能力建设经验。

- 曾作为ONT产品城堡式模块项目负责人,解决0.5mmBGA焊盘间出线问题,提高0.5mmBGA芯片的布局和组装可靠性问题; 高速背板开发工艺负责人,成功解决了60层PCB背板加工难题;曾承担产品无铅切换负责人,带领团队识别风险、制定措施,开展加工验证以及可靠性验证,完成了多种单板无铅验证,无批量问题。

- 承担工艺基础能力建设工作,协同跨领域人员,整理输出DFM相关工作流程及技术规范;负责工艺设计规则优化工作,并实现人工检查到机器检查的转变。

- 曾承担部门人才培养工作,每年组织新员工进行人员培养和课程培训,内容包含:PCB制造,PCBA制作,焊接知识,工艺可靠性知识等。在工艺人才培养方面有丰富经验。

季伸彪|西门子EDA亚太区市场技术工程师

- 2019年加入Siemens EDA, 加入Siemens EDA之前曾经在国内大型EMS公司及国内知名通讯公司任职,深刻了解DFM在PCB设计与制造中的优势,2006年开始从事DFM相关岗位,2011年开始从事Valor NPI技术相关岗位。

演讲简介:

- 电子元件在PCB上的排布越来越密集,电气干扰成了不可避免的问题,所以对叠层的设计和安排显得尤为重要。随着PCB速率和频率不断增加,叠层的正确成为高速设计的基础。PCB改版是研发人员最不期望看到的事情,而PCB叠层问题是造成PCB改版的最常见的原因之一。不良的PCB 叠层设计会导致传输线阻抗失配,参考平面缺失等,并引起严重的信号完整性问题;电源和地层的不合理安排也会引入大量回路电感,引起去耦电容的“失效”;同时叠层设计也是影响EMI/EMC 的重要因素。

- 如何才能减少或者避免因为叠层原因造成的改版?很多公司耗费巨资来购买信号完整性仿真软件,用来模拟信号在实际产品中的表现。叠层的主要挑战是很难建立有效的叠层模型,而不准确的模型会影响仿真精度。影响因素包括:铜厚、层压后的厚度、DK、DF、玻纤结构等。叠层材料的选择很大程度上决定了高速总线的最大长度。因此如果没有准确的材料和叠层参数,将无法在设计的初期实现有效的信号完整性仿真!任何一个参数不当,都会造成损耗模拟的偏差,这样制造出来的实际产品就很难符合预期性能。

- 通过本次研讨会,我们将展示客户如何将叠层设计“左移”到整个设计流程当中,如何在设计初期阶段就开始进行阻抗计算、损耗分析以及叠层规划,如何为PCB前仿和后仿无缝的提供最准确的叠层参数和结构,如何做到叠层设计的“一版成功”。

直播大纲:

- 高速PCB的简介

- 高速PCB的影响因素

- 为什么需要更好的PCB叠层工具

- 高速PCB设计流程中的叠层设计

- 高速PCB叠层设计解决方案

- Z-Planner Enterprise叠层工具演示

- Z-planner Enterprise价值总结

实例一:Z-Planner Enterprise如何与P C B设计流程完美集成,赋能高速PCB叠层设计。

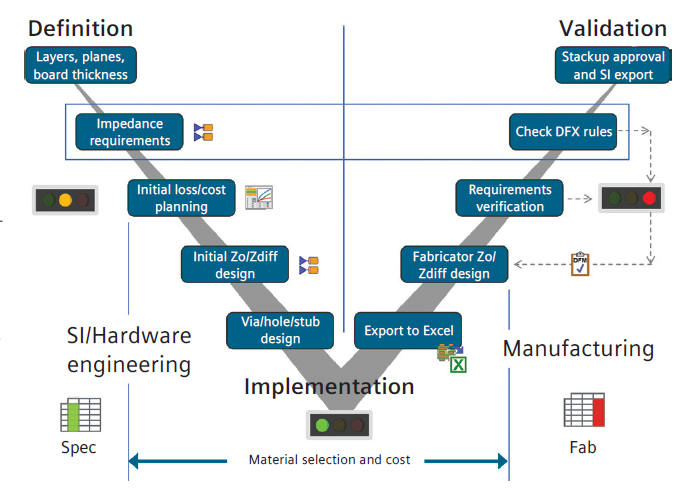

- Z-planner Enterprise不仅用于计算阻抗,还能在设计的初期帮助设计人员定义和优化叠层需求,确保PCB前仿真能够使用一致的叠层设计和最准确的层压参数。Z-planner Enterprise具有的叠层审核功能,可以快速实现多个PCB供应商的生产叠层验证,最终到用于PCB制造的叠层方案,让叠层设计在整个设计过程中形成完整的闭环。

- 此外,Z-Planner Enterprise还具有叠层复用功能,通过在未来的项目中使用经过验证的叠层,极大提高设计团队效率,节省大量的时间和成本。

Z-planner Enterprise 可以很好的嵌入PCB设计流程中

实例二:Z-Planner Enterprise如何全面助力整个设计团队

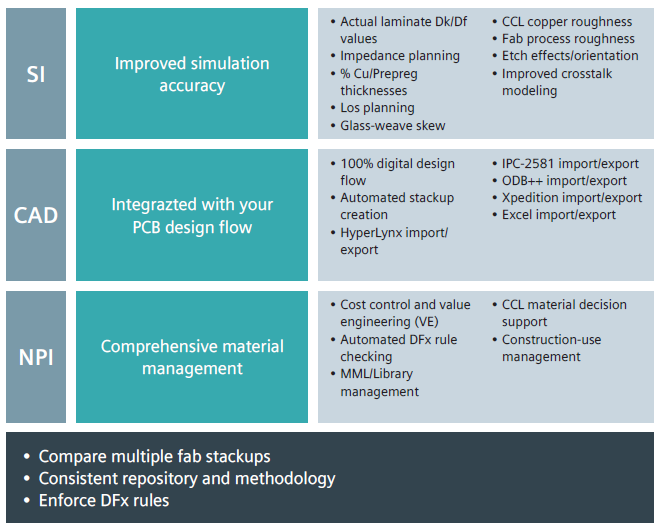

- Z-planner Enterprise能够助力于整个设计团队。例如:新产品导入(NPI)工程师可以从Z-planner Enterprise导出准确的Excel格式的设计叠层,发送给每个PCB制造商。PCB制造商收到设计叠层后,结合生产能力和工艺要求,将最终生产的叠层反馈到Excel格式的叠层方案中,以导入Z-planner,然后在Z-Planner中执行相应的多达33项的叠层相关的DFM(可制造性设计)和DFSI(信号完整性设计)检查。

- 硬件设计团队可以使用Z-planner Enterprise 进行自动化叠层设计。自动化的叠层设计基于软件内置和实际材料特性的阻抗分析模块、损耗分析模块,同时会考虑PCB材料库中的与频率相关的Dk、Df和铜箔粗糙度参数等信息。

Z-planner Enterprise使整个设计团队受益

实例三:Z-Planner Enterprise集成哪些主流PCB材料库,如何全方位满足客户需求

- Z-planner Enterprise中最重要的功能之一是PCB材料库,目前Z-planner Enterprise集成了欧美以及亚洲地区常用的板材供应商的材料库,包含150多个系列的板材数据,可以满足不同客户对PCB材料的需求。这些数据均来自全世界主流的制造商,包括但不仅限于AGC、Nelco、EMC、斗山、ITEQ、南亚、松下、生益、TUC和Ventec。

- 这使得在选择材料时,用户可以充分考虑频率、树脂含量、玻纤结构和层压后PP厚度等参数,并且Z-Planner Enterprise内置筛选功能,可以让你快速找到想要的材料。与此同时,Material Matching TM功能可以根据所选的材料参数快速替换和更新叠层设计,并提供全面的雷达图,包括Dk、Df、Tg、Td、z-CTE和x-y CTE等参数。

Z-Planner Enterprise集成9家主要层压板制造商的材料库,您可以随时随地在材料库中查看各种材料参数

专题演讲特色:

- 如何利用完整的材料库,选择最合适的PCB材料

- 如何实现叠层设计中损耗和成本的权衡

- 如何快速创建高复杂度、高堆叠的高速PCB叠层

- 如何确保多家PCB供应商之间生产叠层的一致性

- 如何提供最准确的仿真数据,做到叠层设计的“一版成功”

适合对象:

- 信号完整性工程师

- 硬件工程师

- PCB材料专家

- PCB设计工程师

- NPI工程师

- 工艺工程师