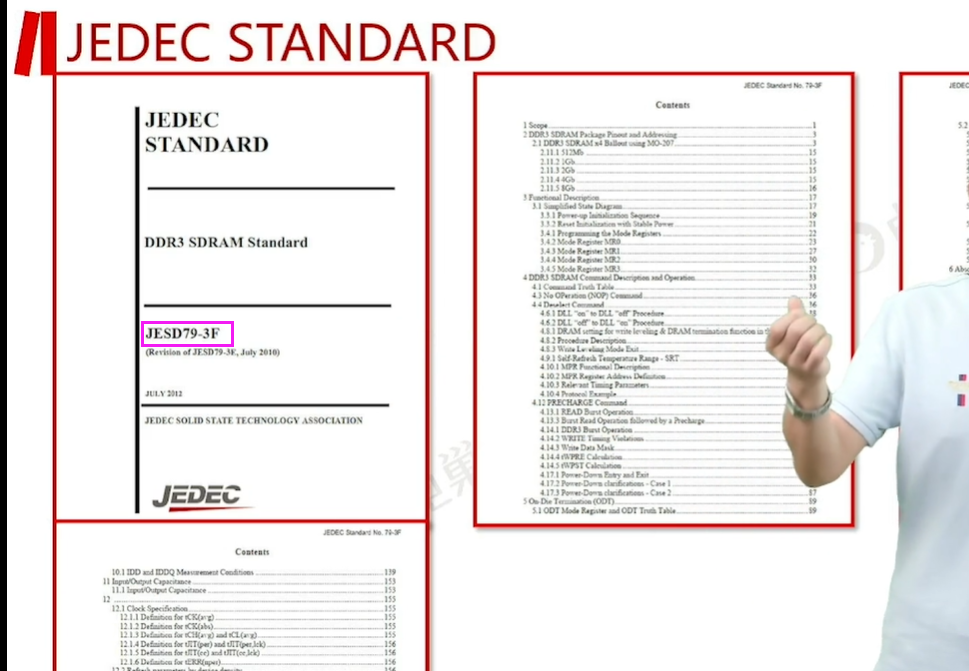

DDR协议仅是针对DDR的标准;

DDR协议仅是针对DDR的标准;

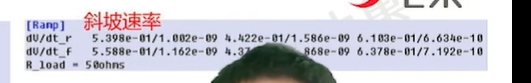

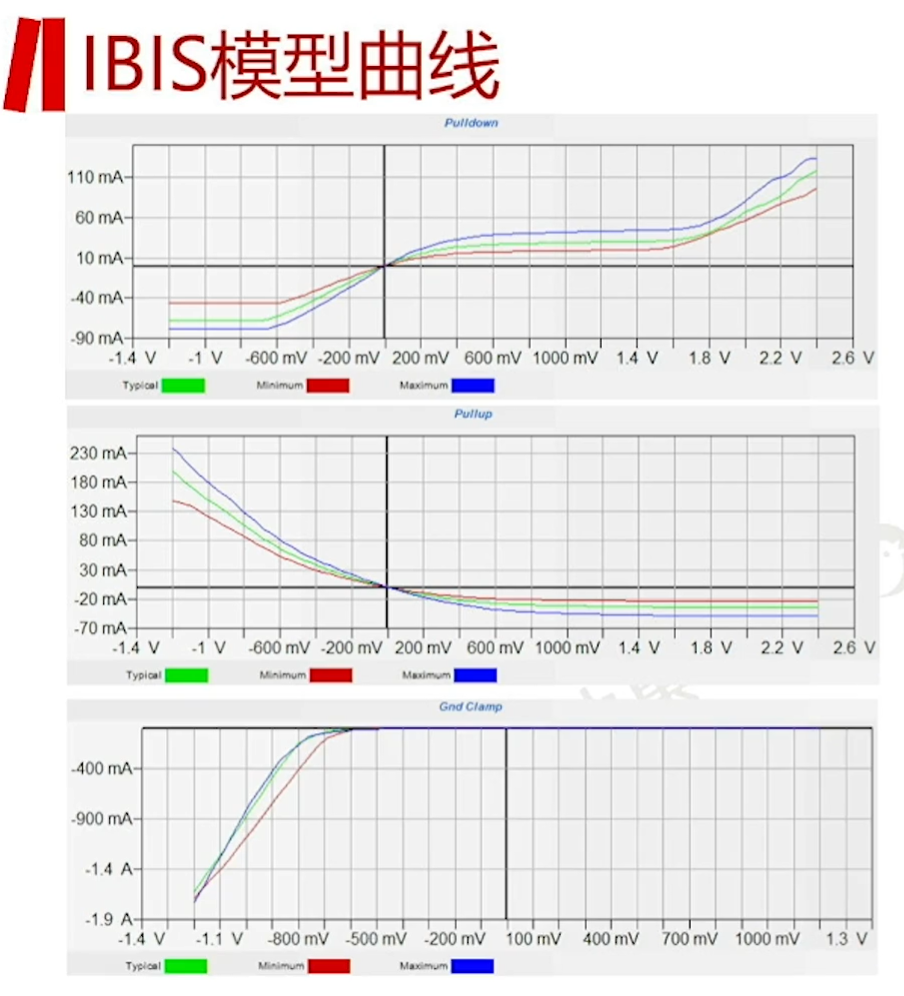

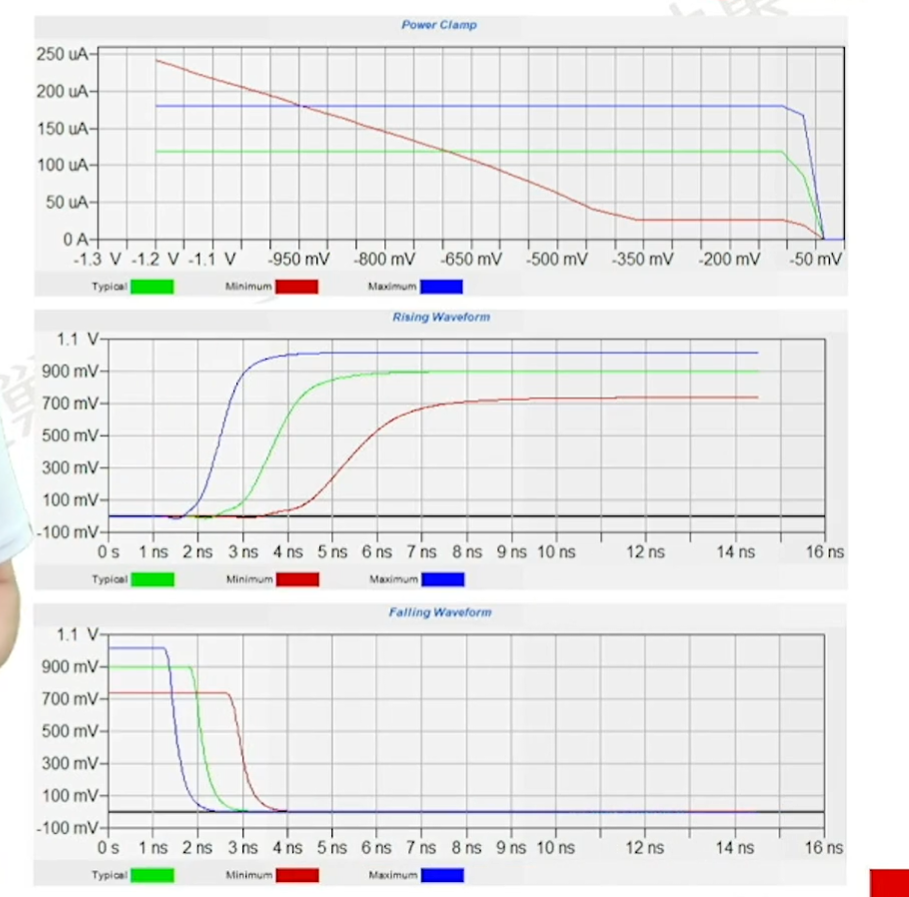

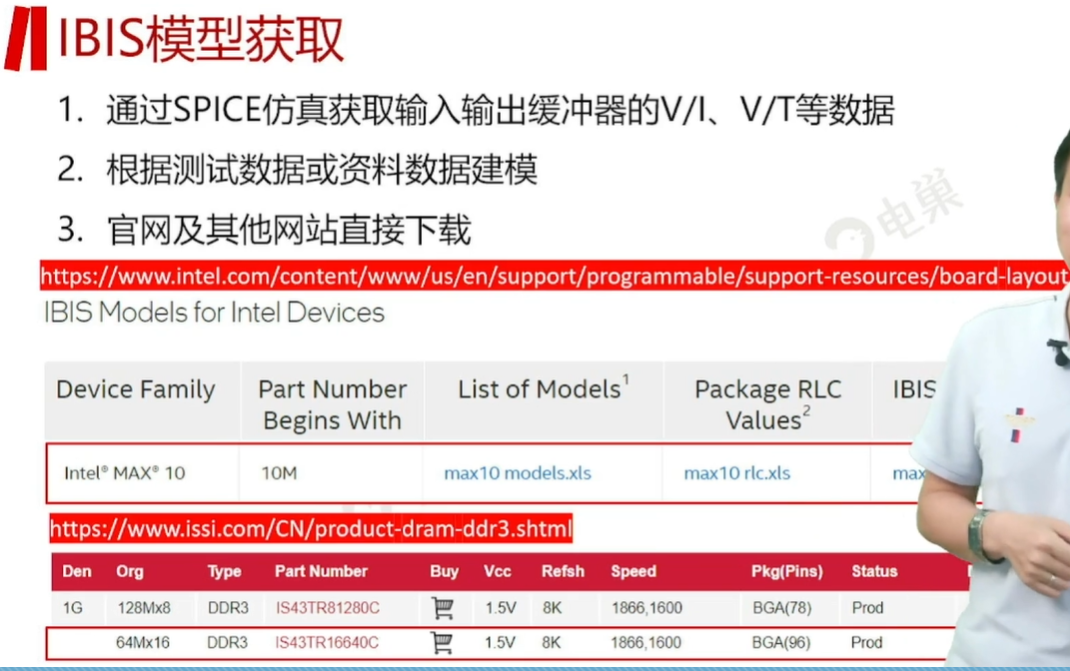

V/I V/T曲线:

曲线类型:

所有曲线过零点,电压电流

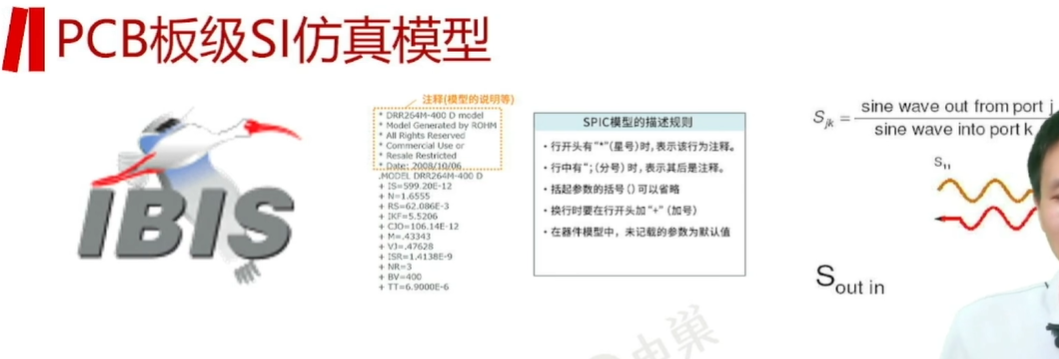

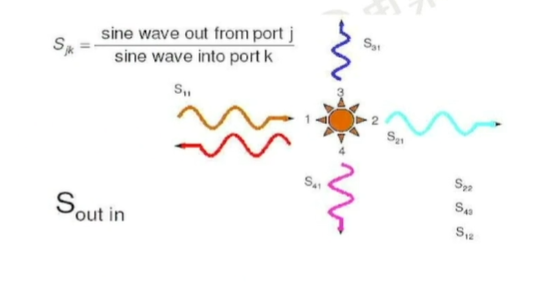

S参数 无源部分 阻容感提取使用;

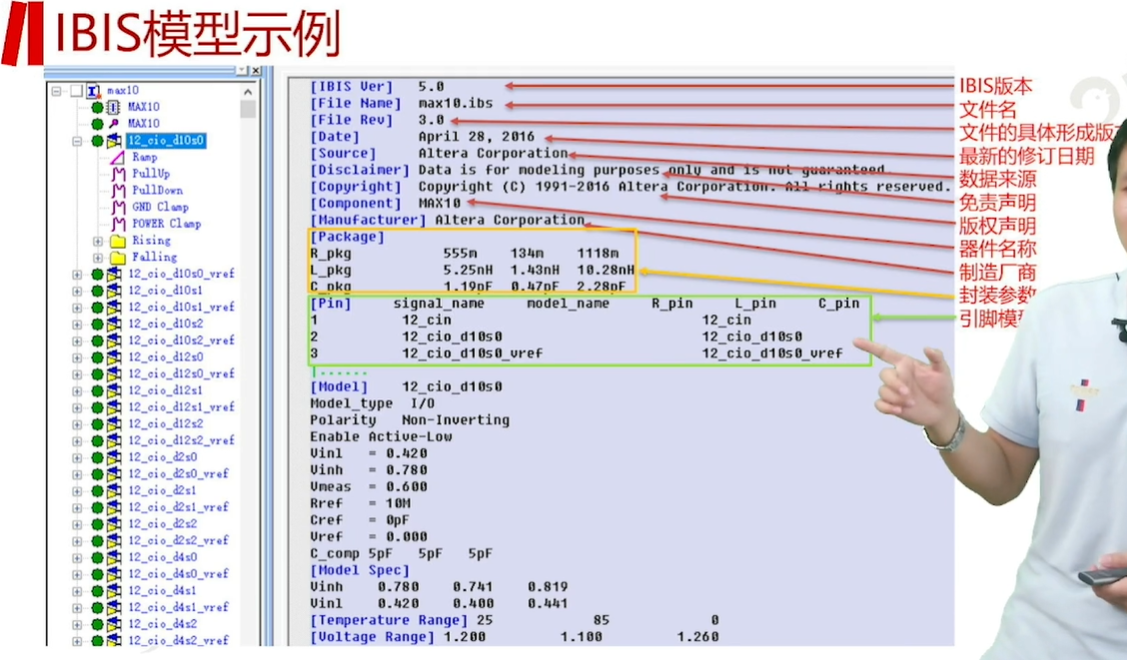

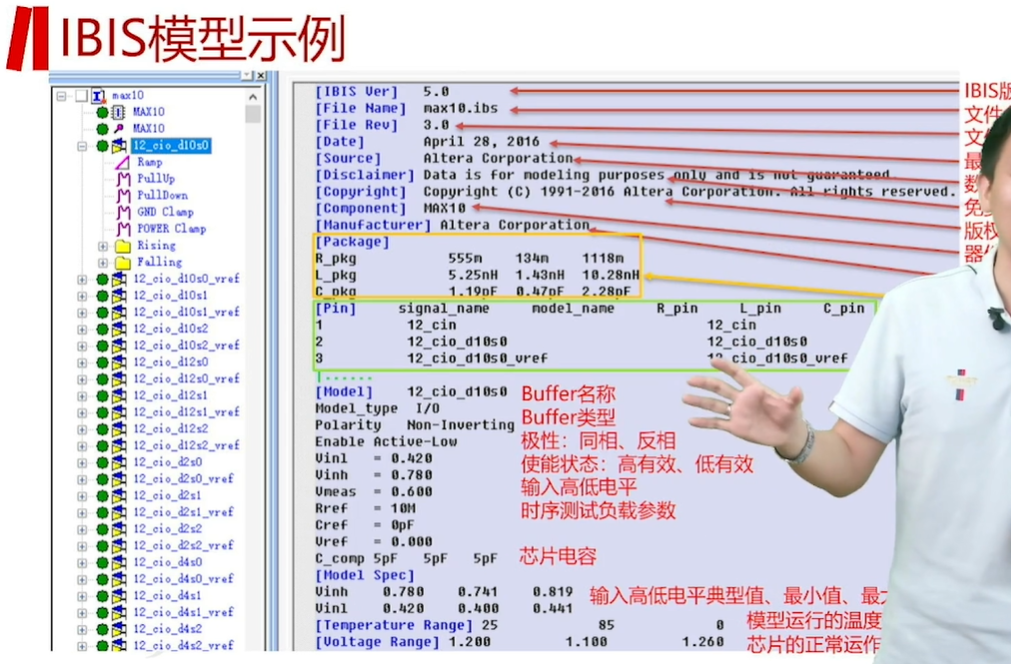

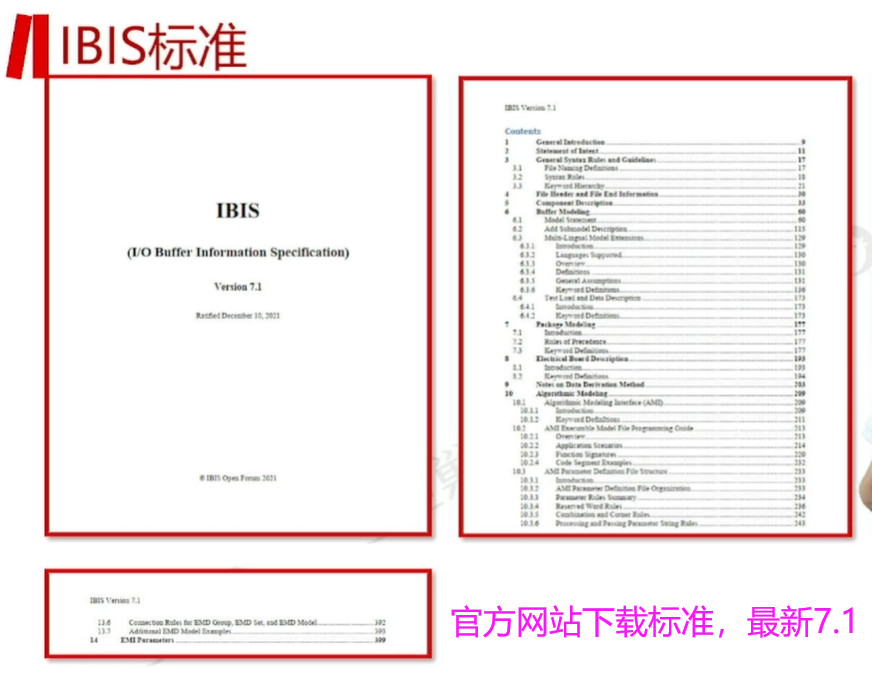

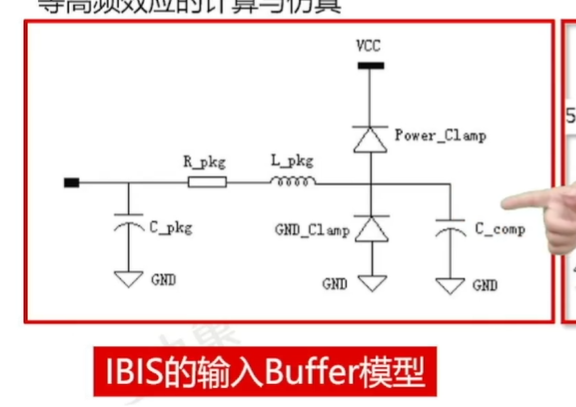

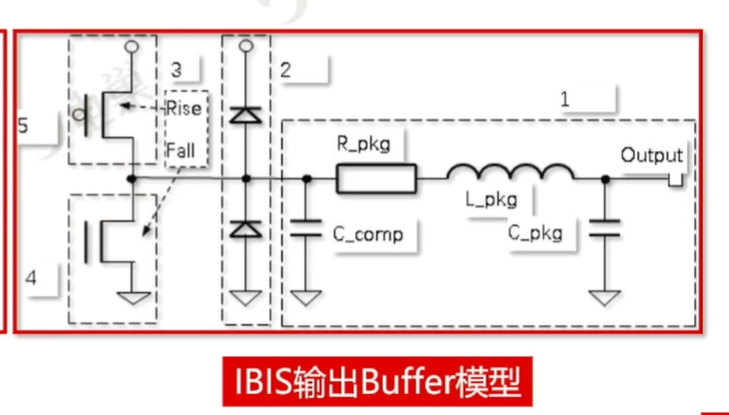

IBIS描述的是I/O Buffer的模型;

总结:

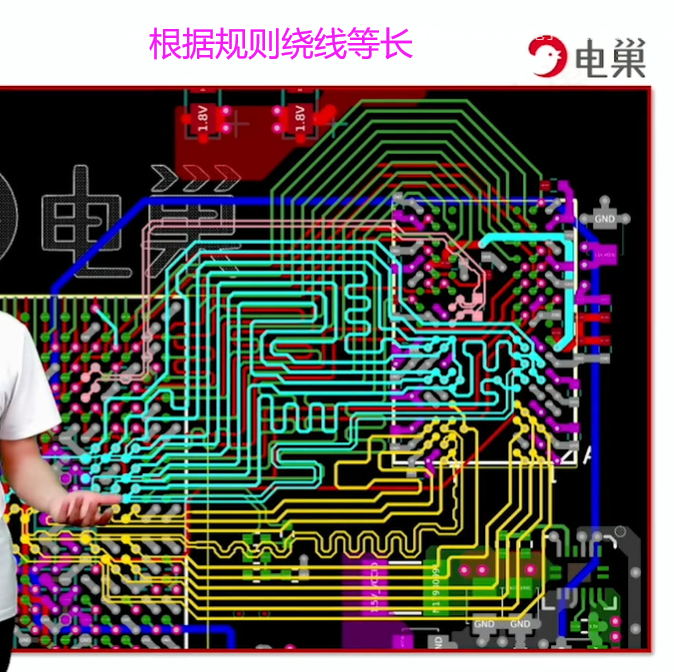

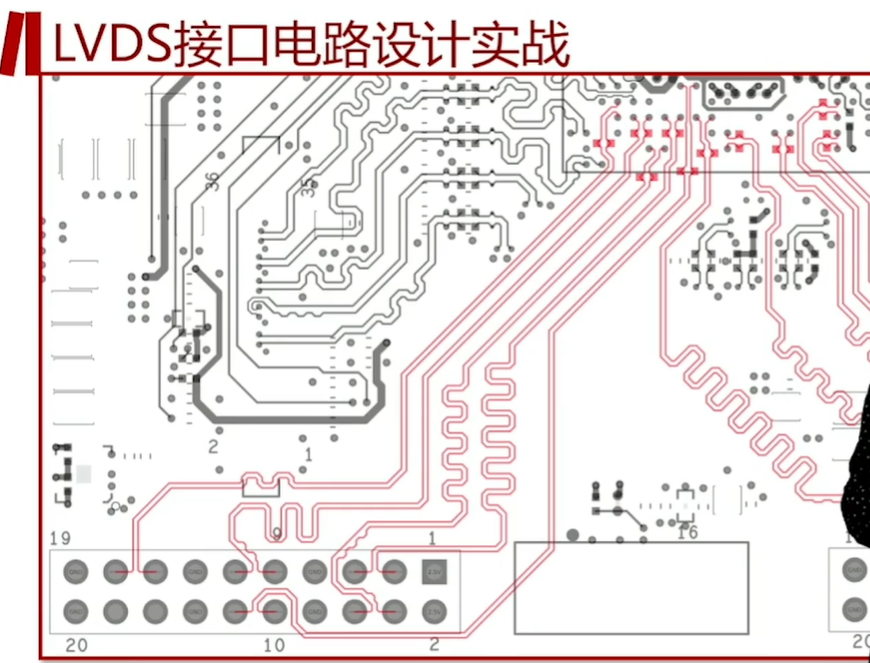

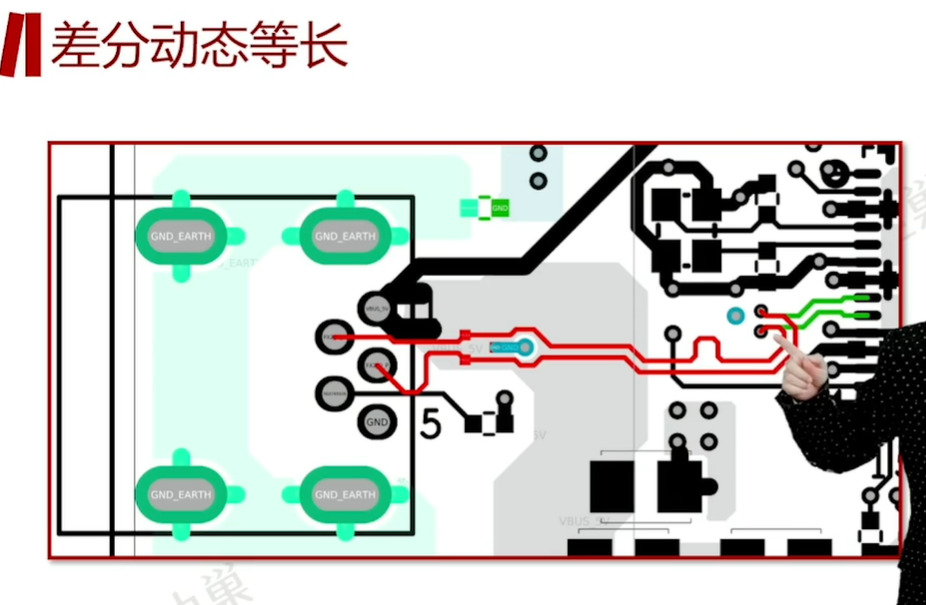

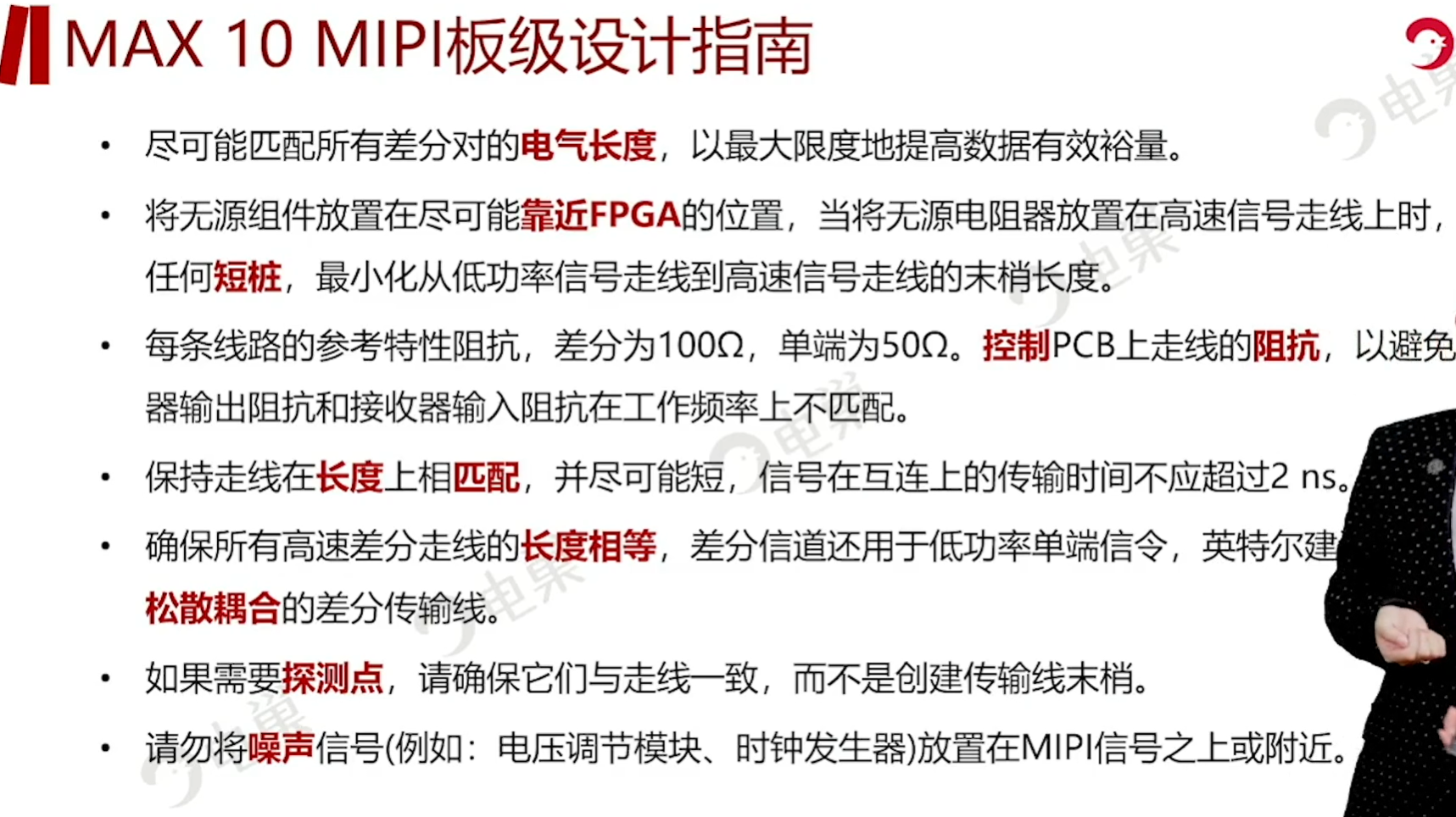

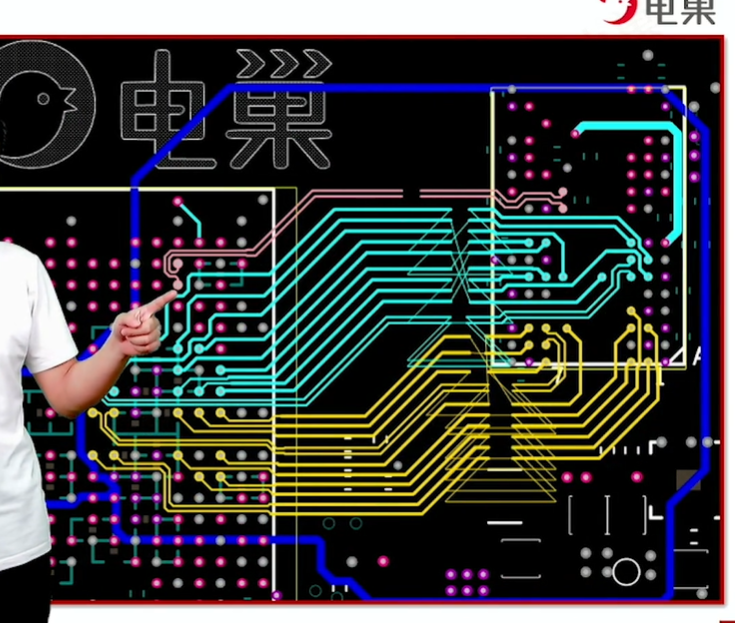

差分对内做动态延时(相位)等长,哪里不等长就近补偿回来,信号在5Gbps以下大波浪小波浪都可以,大于5Gbps采用小波浪控制差分对的相位等长;

PCIE AC耦合电容位置:

通过连接器接口接出去的情况下放在发送端的连接器位置;

通过PCIE两个芯片直接相连的话,放在发送端;

非明确要求,尽量不要放在发送端。

端接电阻靠近芯片;

注意过孔残桩;

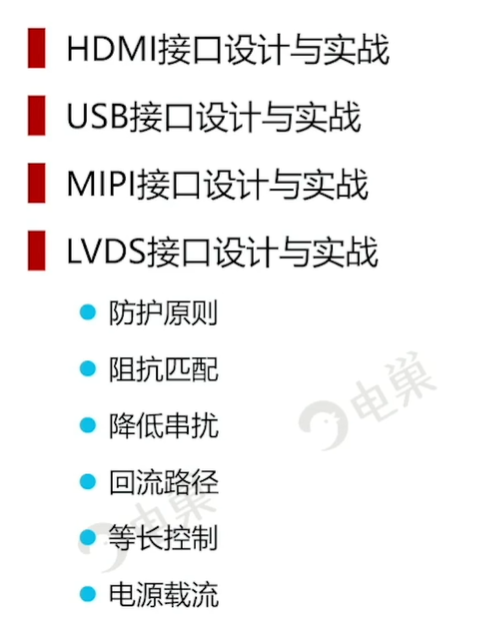

LVDS设计指南:

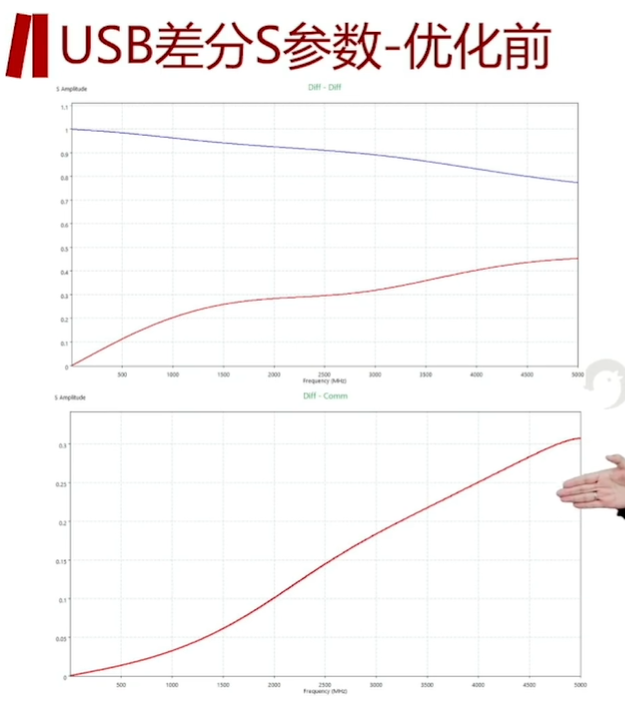

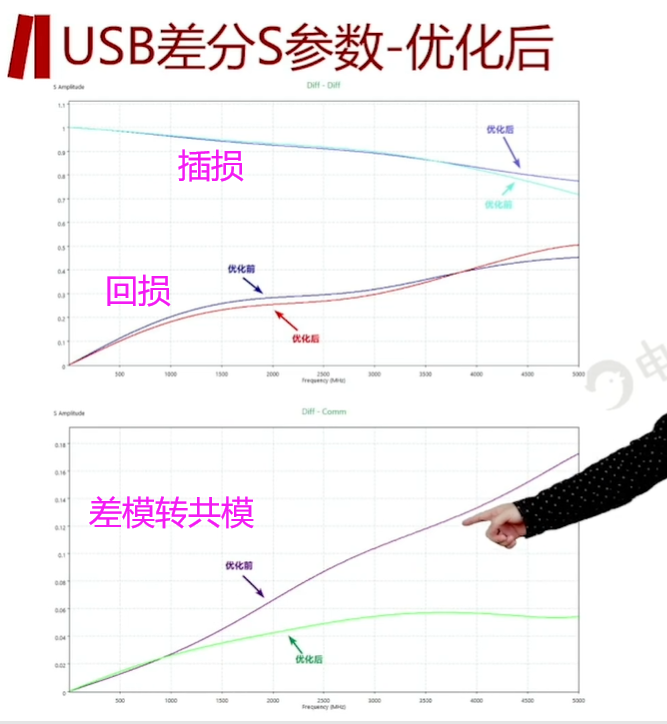

USB设计注意等长动态补偿,减小相位误差,保持相位一致;

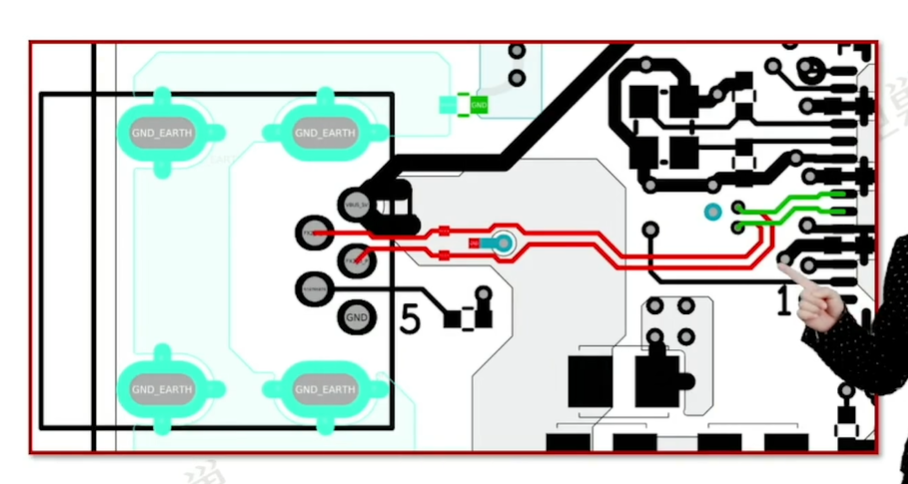

对外接口注意共模辐射;

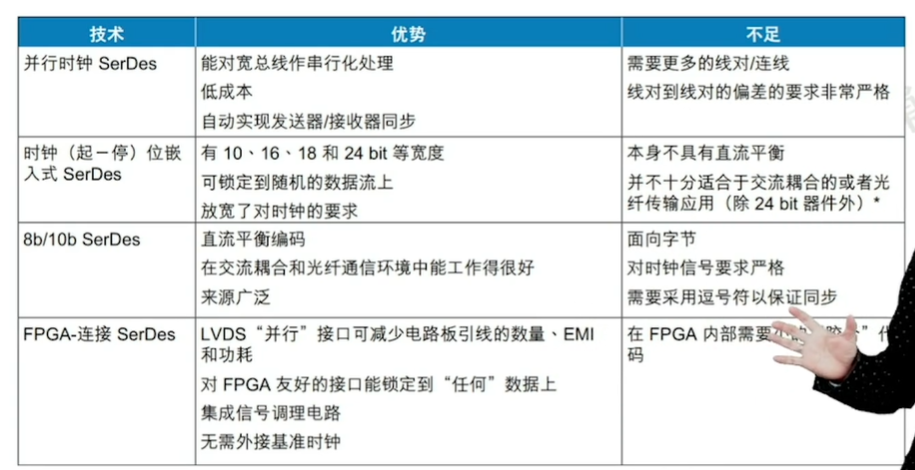

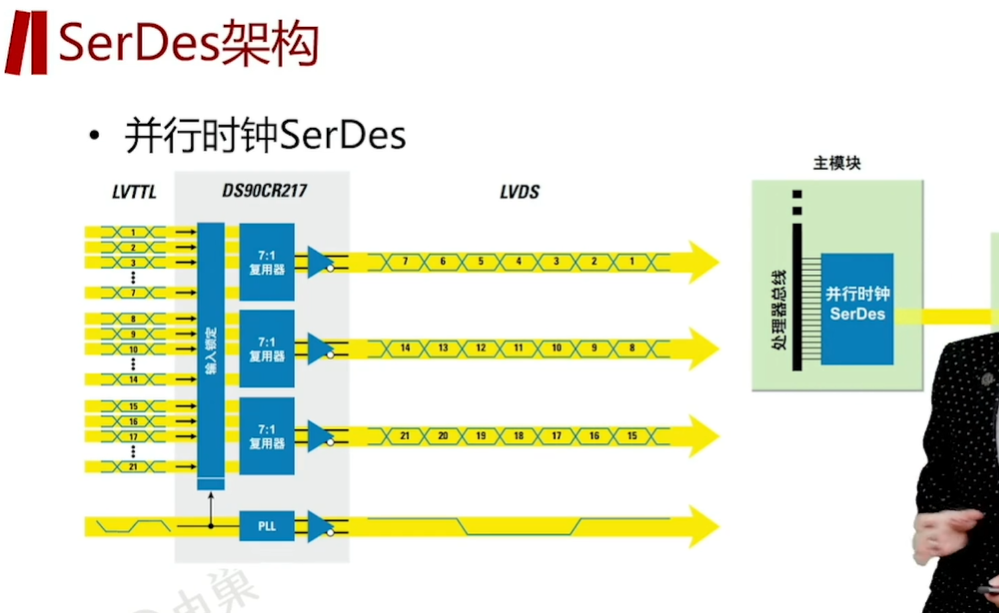

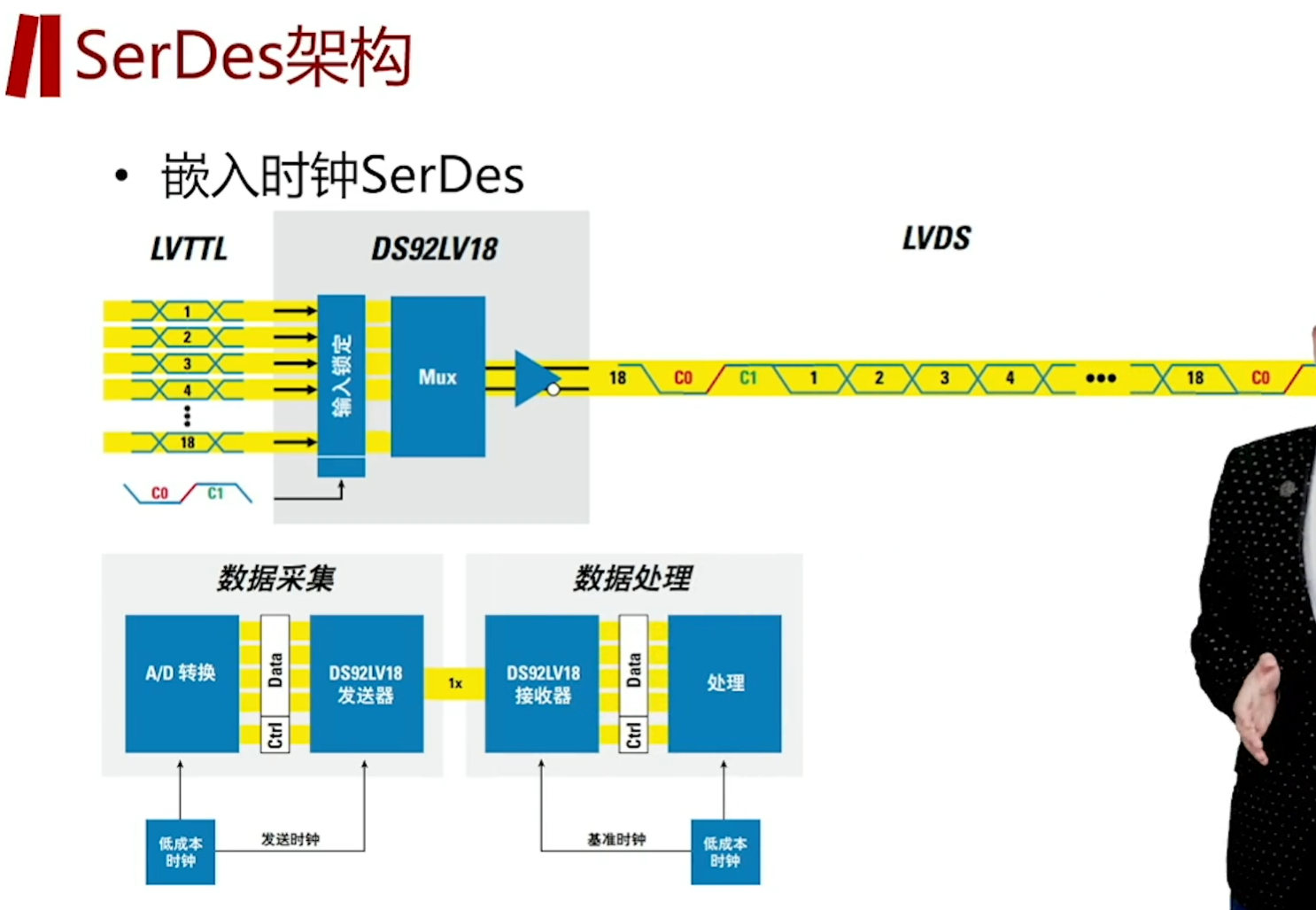

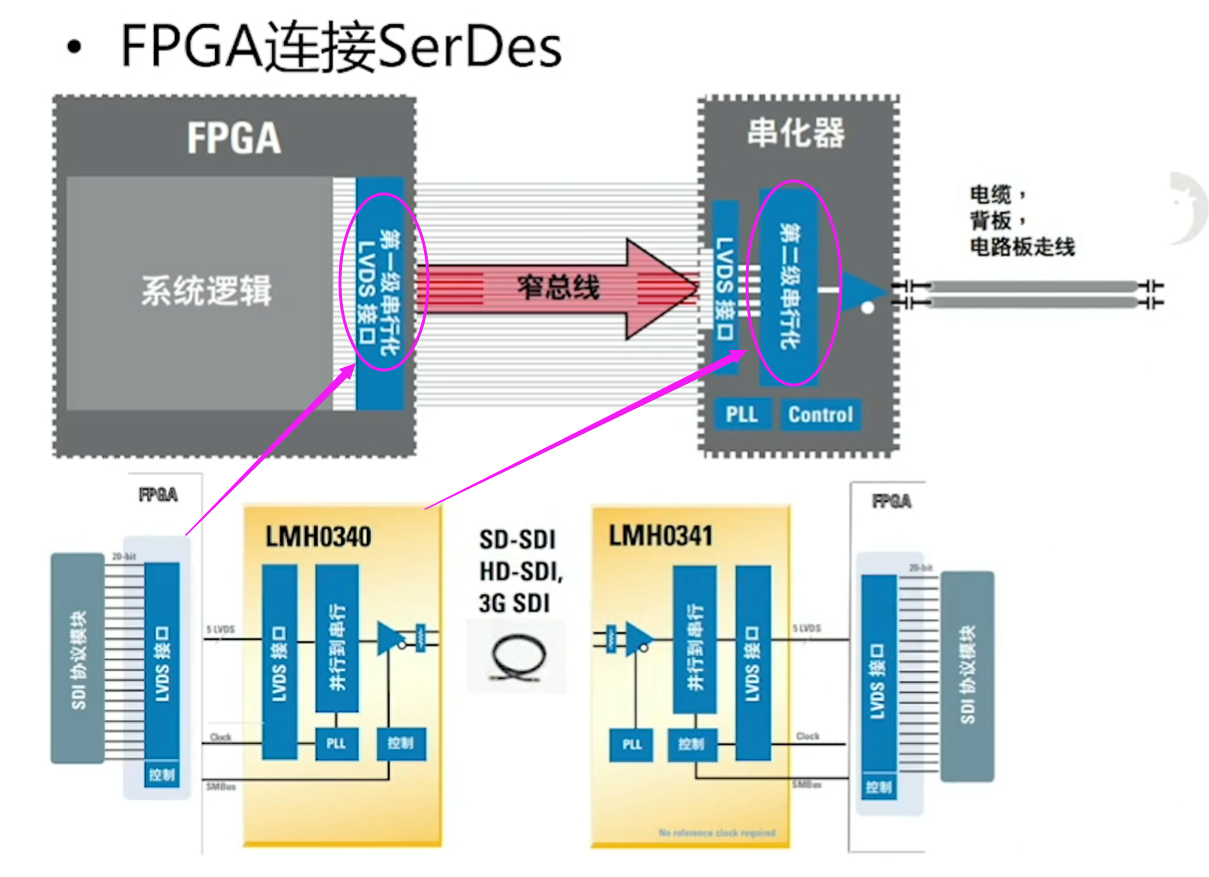

SerDes架构总体比较:

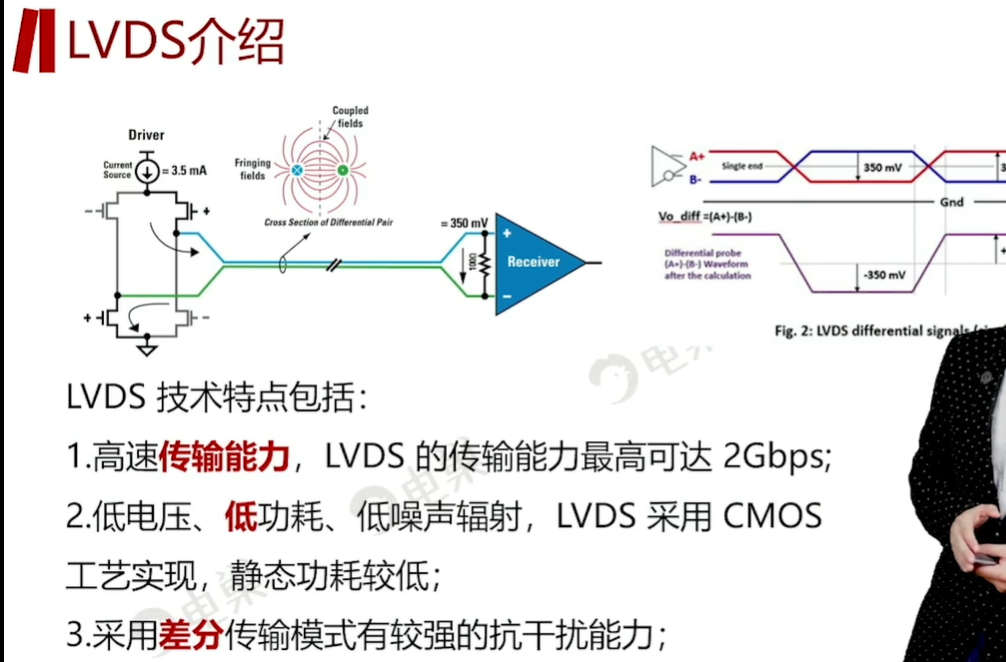

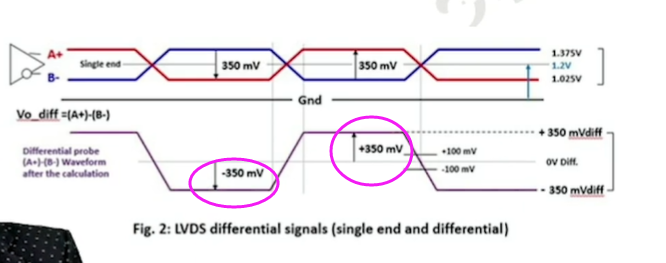

LVDS结构介绍:

端接电阻尽可能的靠近接收端,端接电阻流向判定信号0还是1,由正脚流向负脚判为1,由负脚流向正脚判为0。

LVDS:

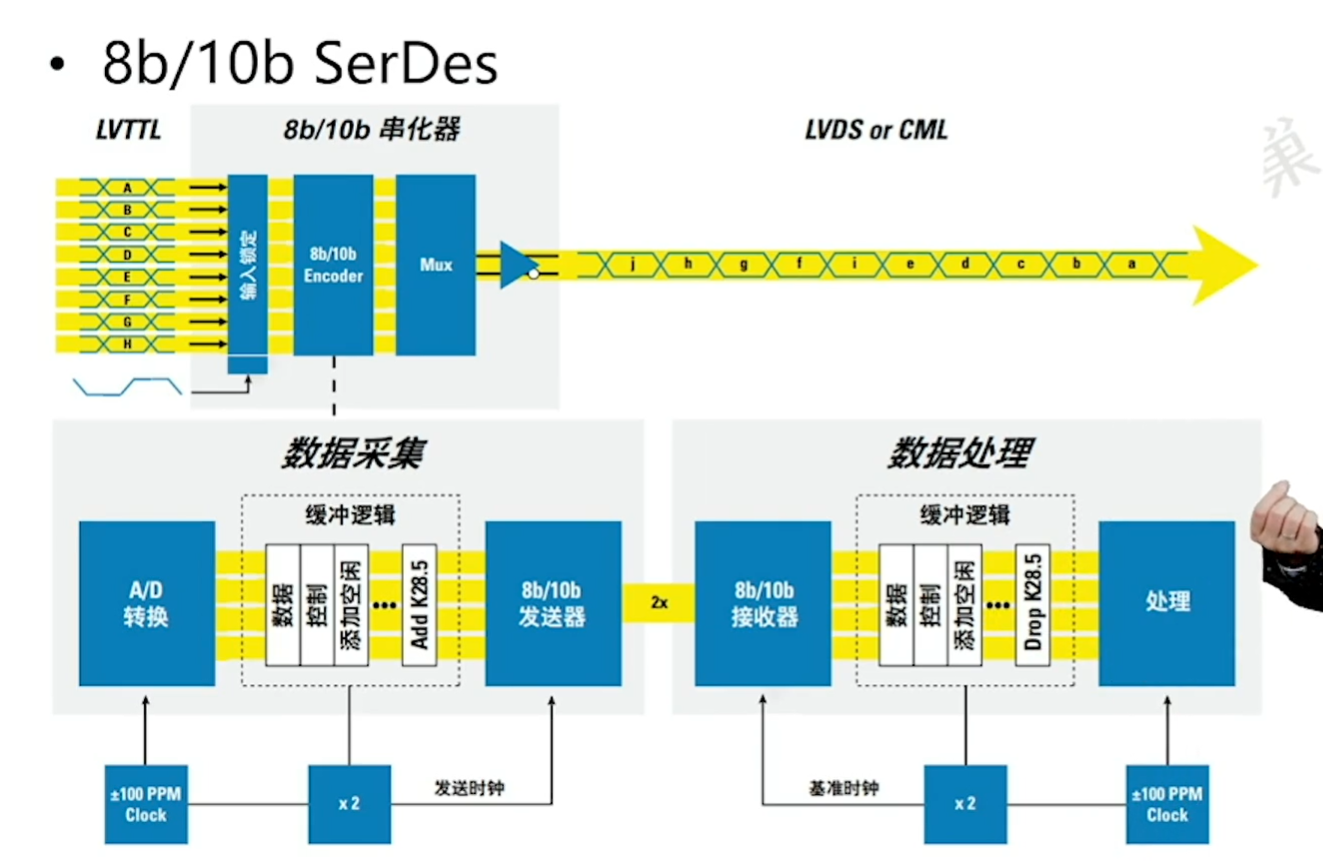

ser串化,des解串;

并行时钟serdes需要单独的伴随时钟线;

嵌入式时钟serdes信号线上拥有基准时钟;

8b/10b会用于USB/PCIE

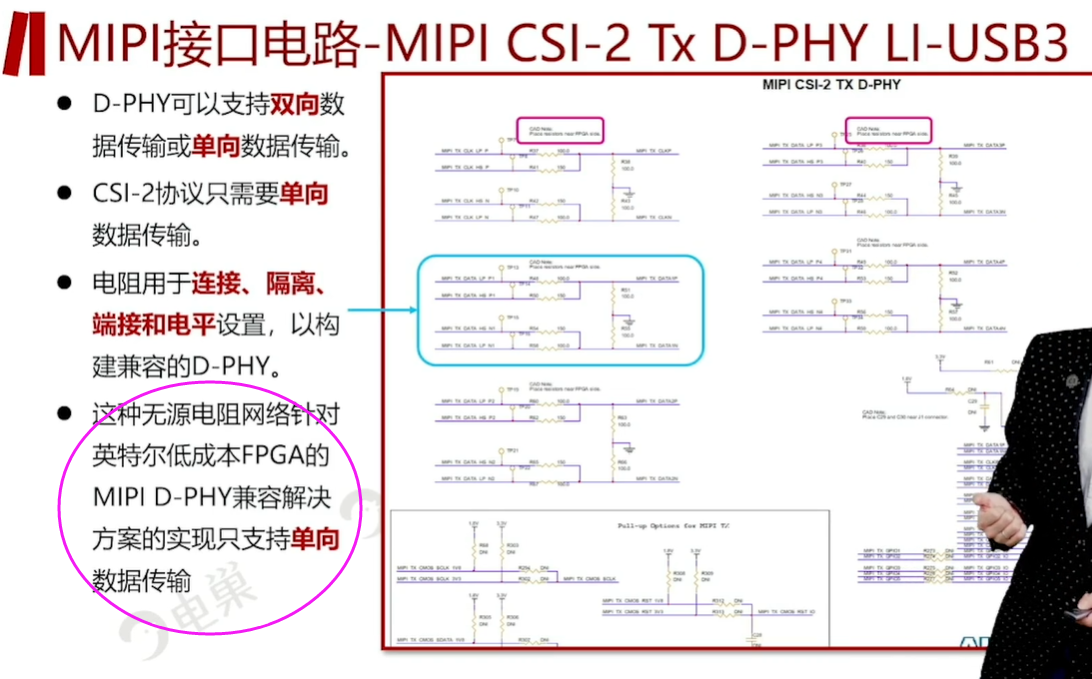

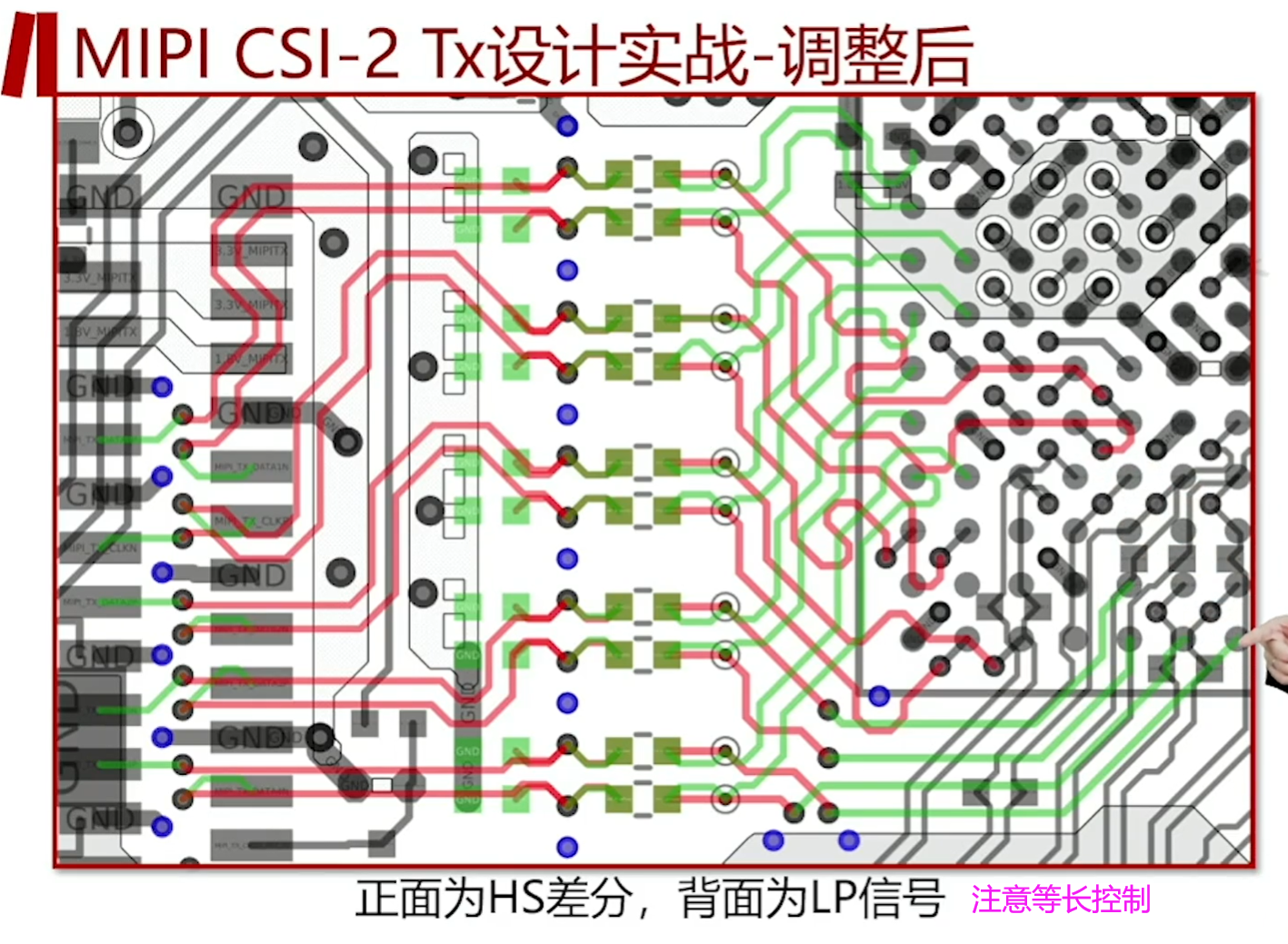

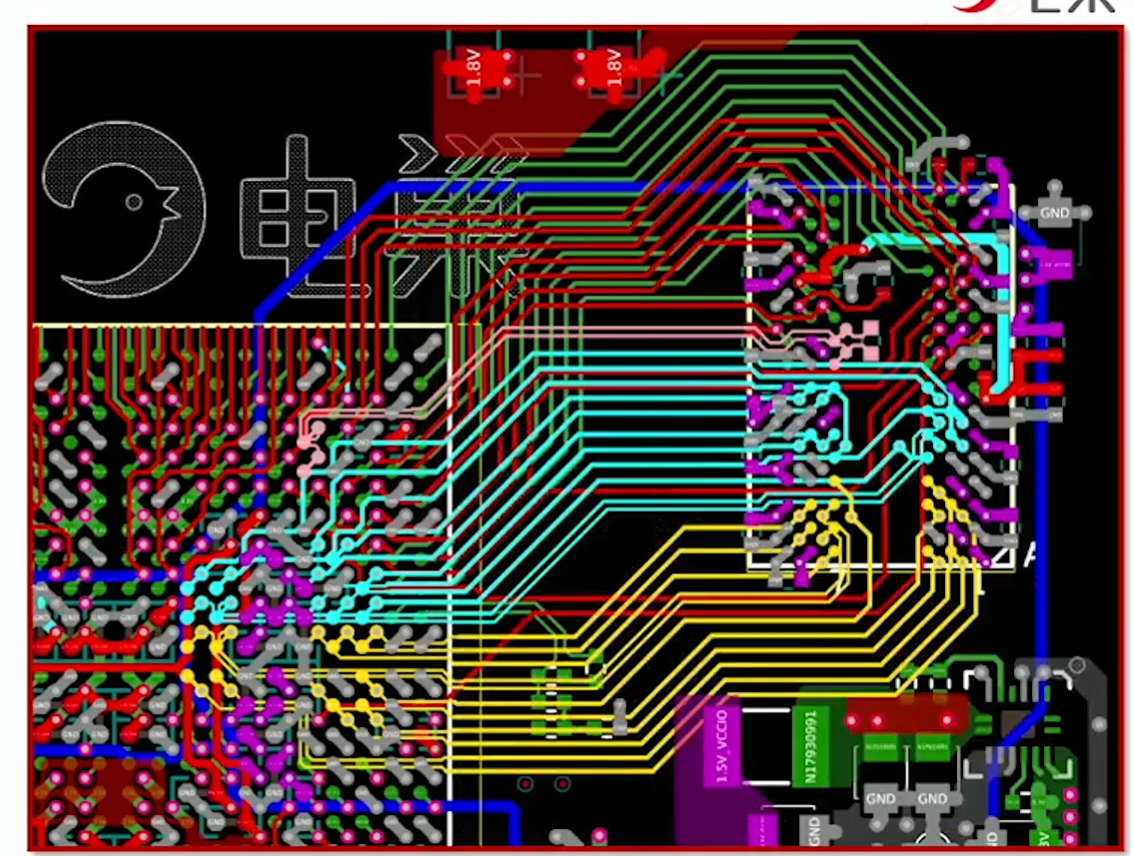

按照设计要求:高速走差分,低功耗低速走单端,背面红色进入芯片部分

MIPI结构上分为物理层、协议层、应用层;

D-PHY:

高速HS模式差分传输80M-1Gbps,低功耗LP模式单端传输<10Mbps。

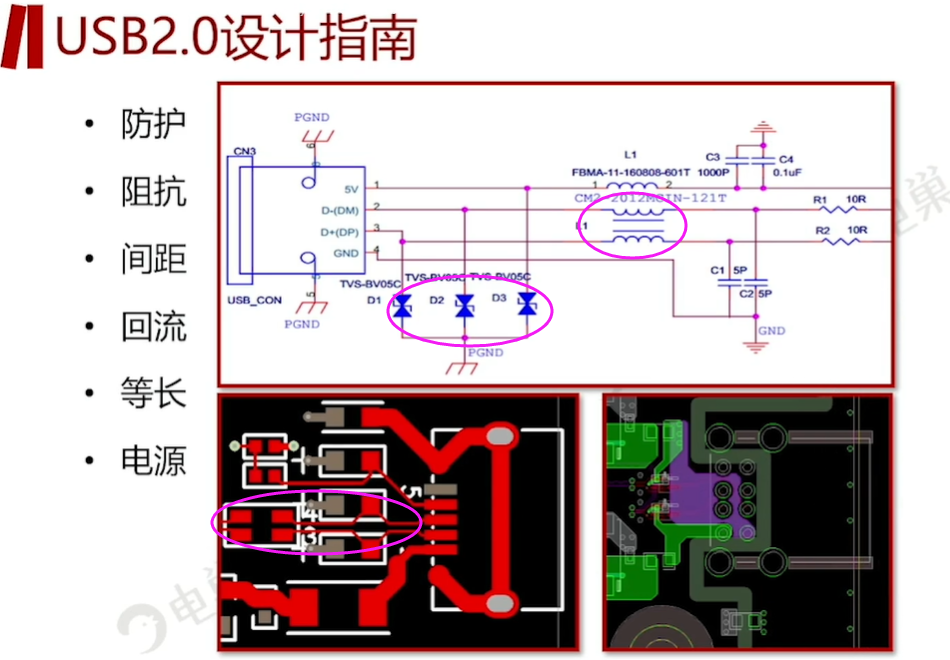

USB2.0设计指南:

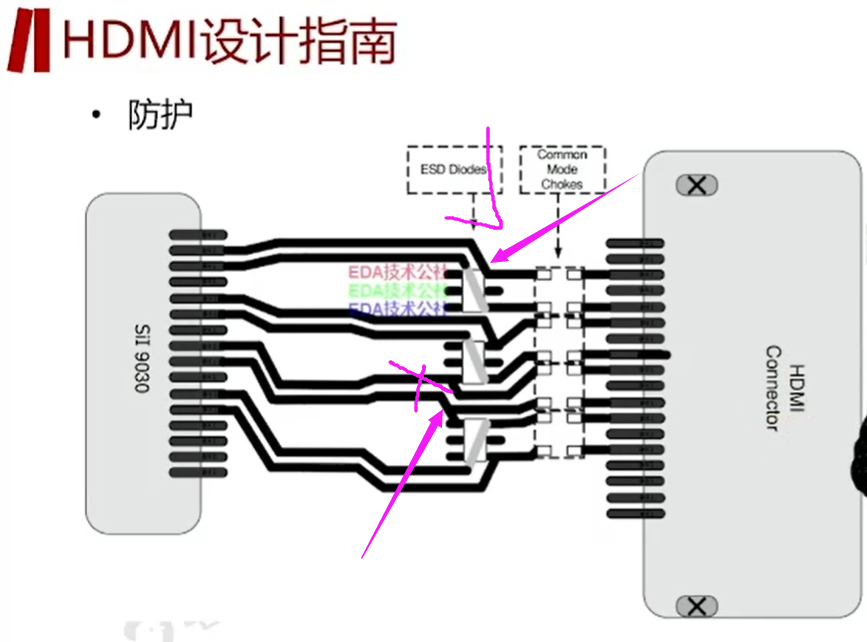

防护设计ESD+共模电感;

阻抗设计为90Ω;

等长控制在±20mil以内;

电源电流500ma,走线15-20mil;

USB3.0及以上要考虑接口插件孔的残桩对速率的影响;

USB3.0设计指南:

防护设计ESD+共模电感;

阻抗设计兼容USB2.0那组为90Ω,3.0收发采用100Ω;

间距最好做到20mil以上,换孔换层均以地平面为参考;

等长设计做到对内±5mil以内,对间单独收发不受影响;

电源电流1A左右,线宽要50mil以上。

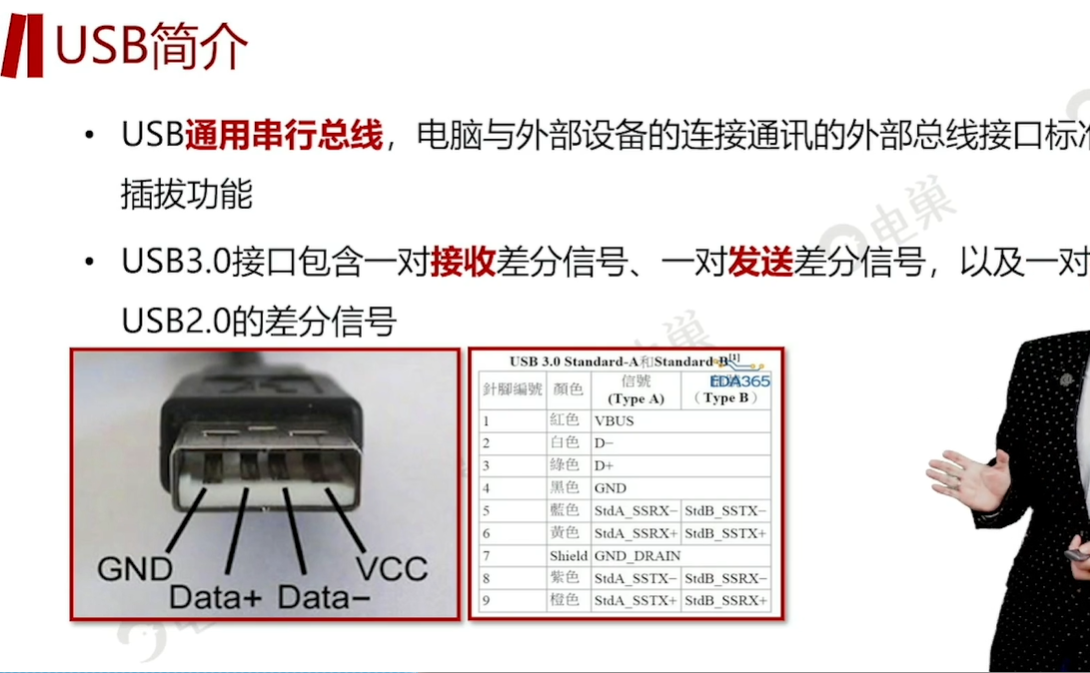

USB 通用串行总线

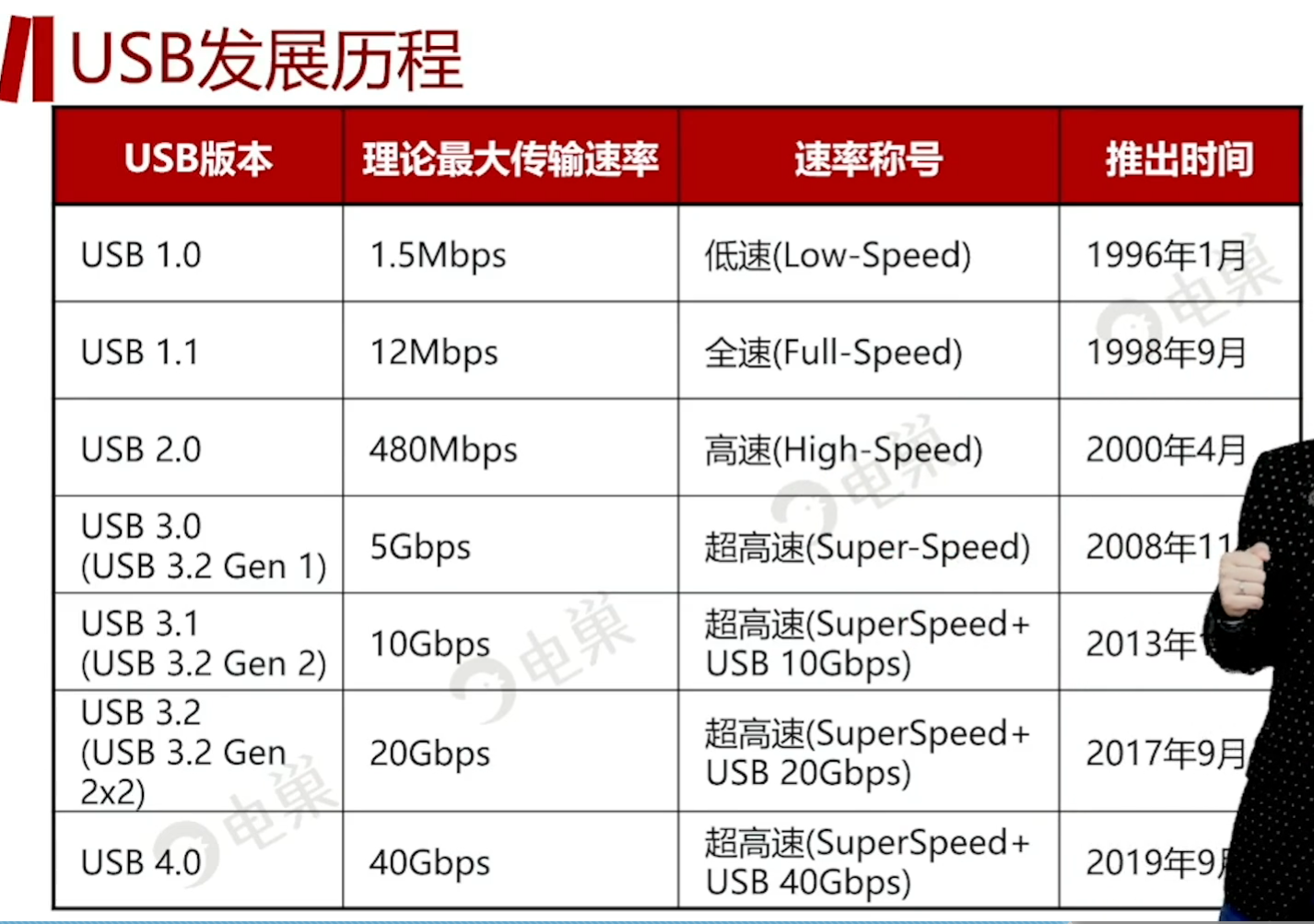

USB3.1有单lane和双lane两种,单lane的是一组10Gbps的传输速率,双lane的是2组分别为5Gbps共10Gbps的传输速率;

USB3.2有两组USB3.1单lane 10Gbps组成,两对发送两对接收,单组实现10Gbps的传输速率,共20Gbps的传输速率。

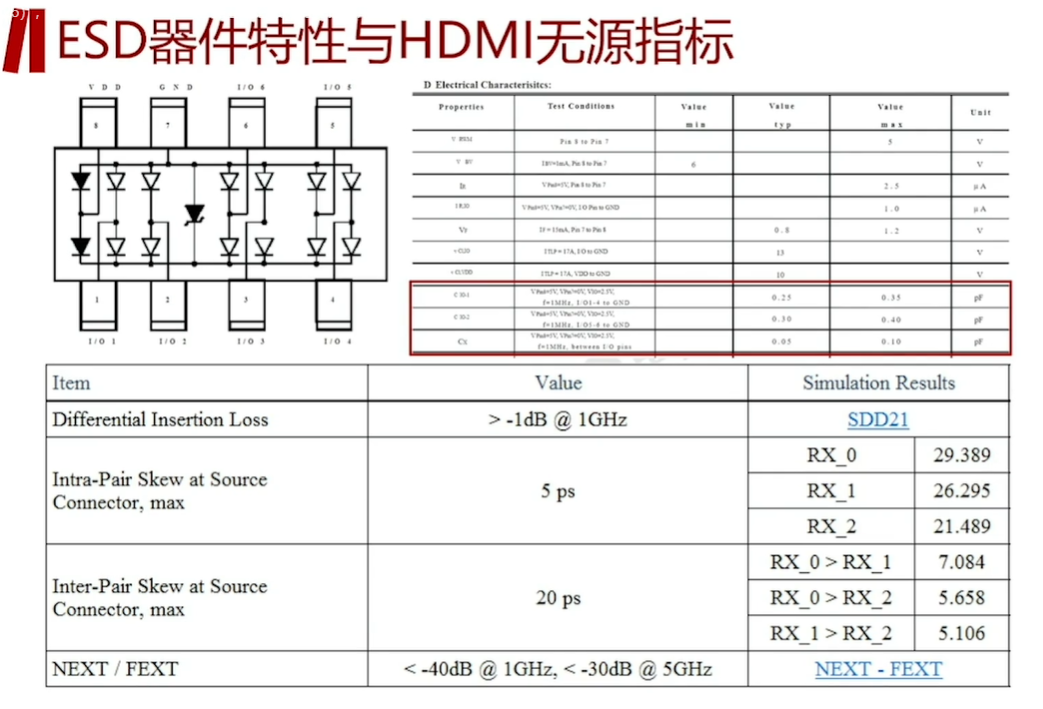

第一次仿真ESD寄生电容设置的是10pF,插损为-10dB,第二次仿真设置为0(不带ESD器件),第三次设置为带ESD器件的0.35pF,仿真结果插损为-0.3dB,满足要求

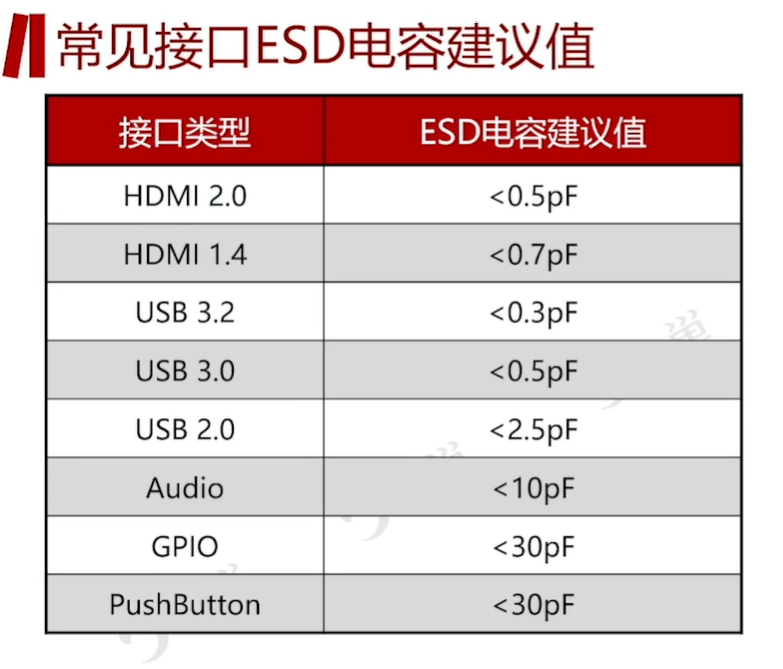

高速信号考虑ESD寄生电容值,下图为参考表:

根据上次仿真结果可知,串扰-50dB以下是满足要求,插损不能满足需求,导致眼图闭眼,需要填入ESD寄生电容进行第二次仿真。

如果对内信号在ESD期间上是交叉的,可以对换ESD管脚,使布线比较顺畅,少打过孔;

电源滤波器件靠近芯片管脚摆放;

差分对内对间注意间距,降低串扰;

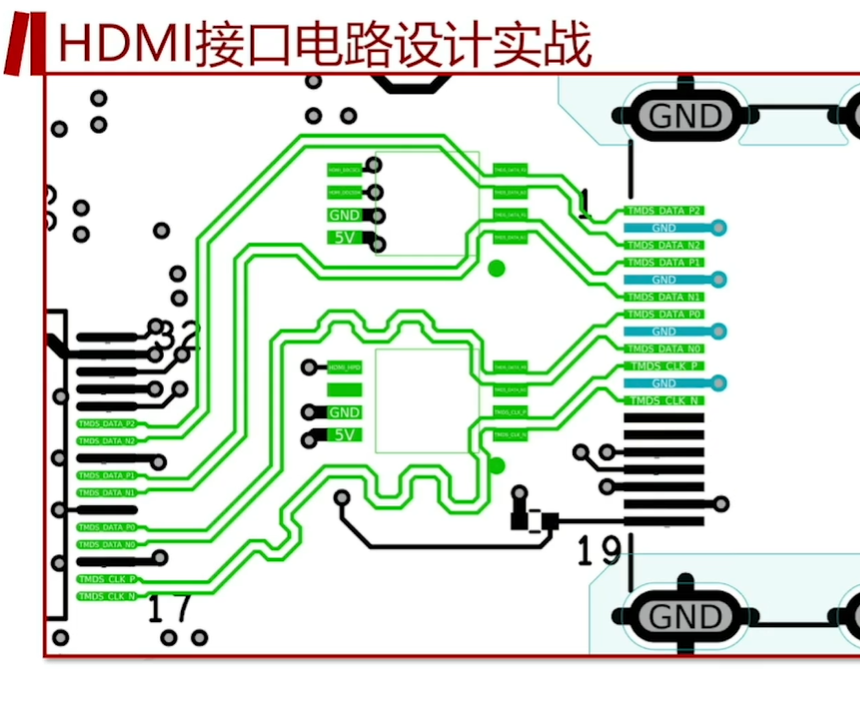

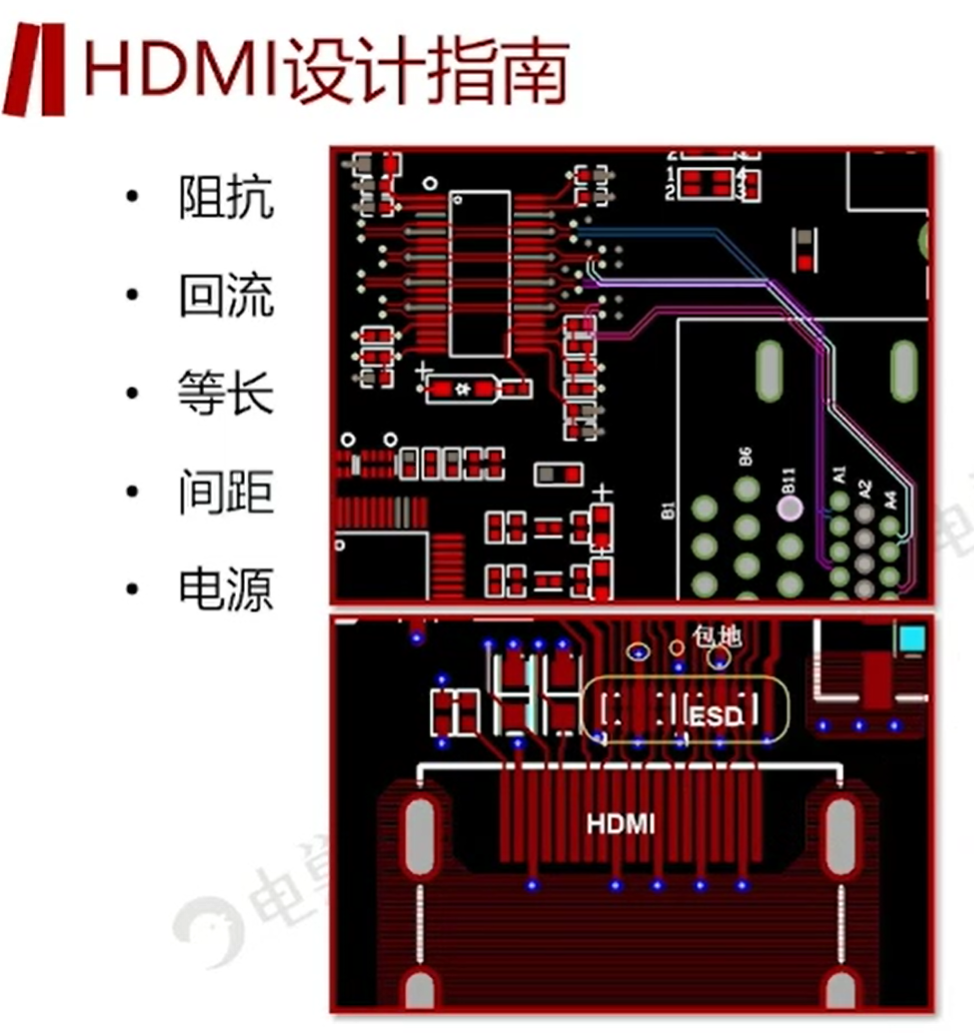

HDMI设计指南:

先过防护器件再接内部器件管脚;

差分阻抗控制100Ω,HDMI2.0/2.1高速传输时不仅走线要考虑,过孔和插件管脚也要考虑阻抗;

回流优先使用地平面,换层时要考虑参考面;

速率越高对内等长要求越高,比如HDMI1.4对内等长考虑小于10-20mil长度差距,超过5Gbps以上时不仅对内等长还要考虑相位等长,进行相位补偿,哪里不对补哪里;

对间间距拉到15-20mil,和其他信号之间间距20mil以上为好;

焊盘出线宽度不能超过PIN宽度;

HDMI

一对时钟和3对数据,4组差分信号

常用HDMI1.4/2.0,现在4K/8K电视会采用HDMI2.1

数据线同层同组去走线

A12被挡住无法从内部底层顶层走线,和C22空脚互换;

S绕线时小波浪绕线,线间间距时4W,线边间距为3W: