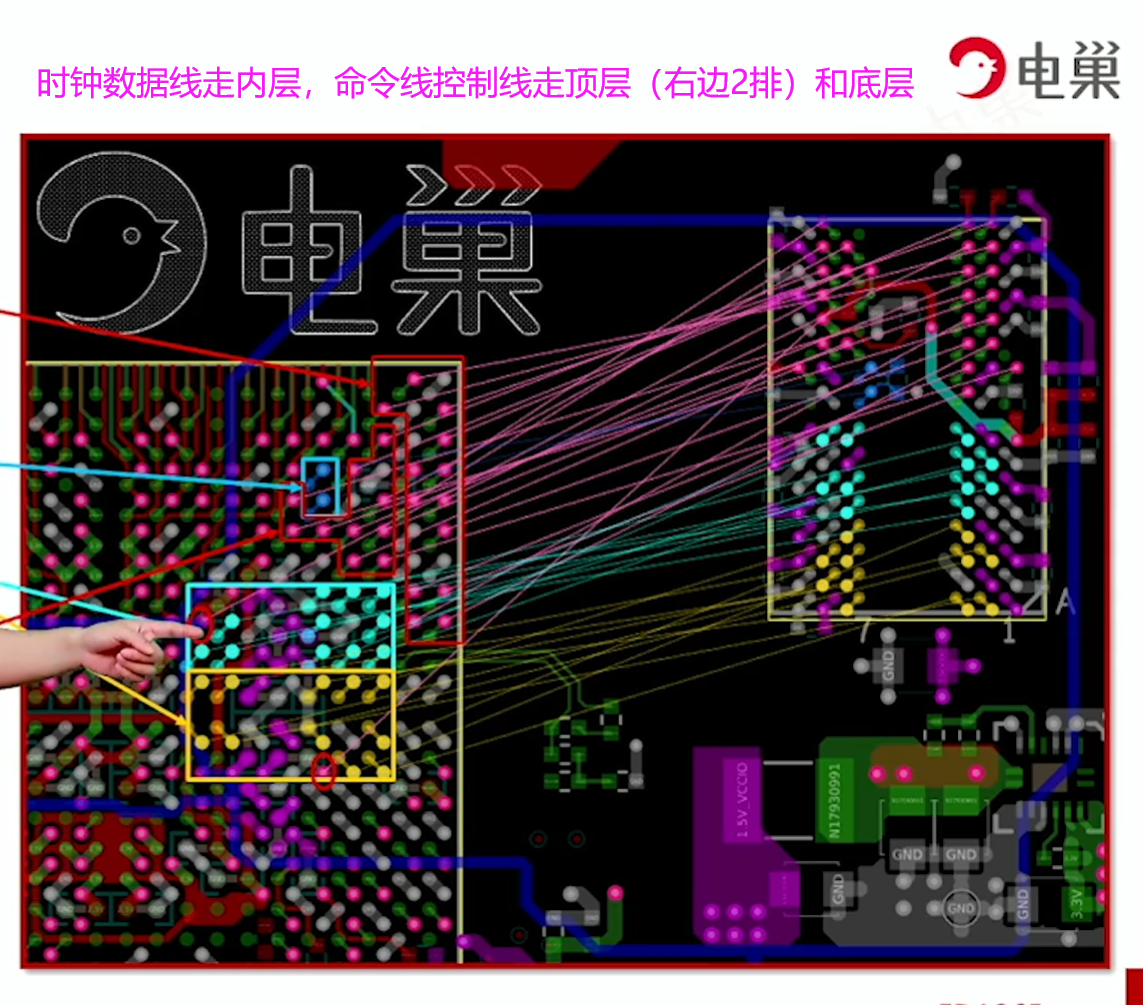

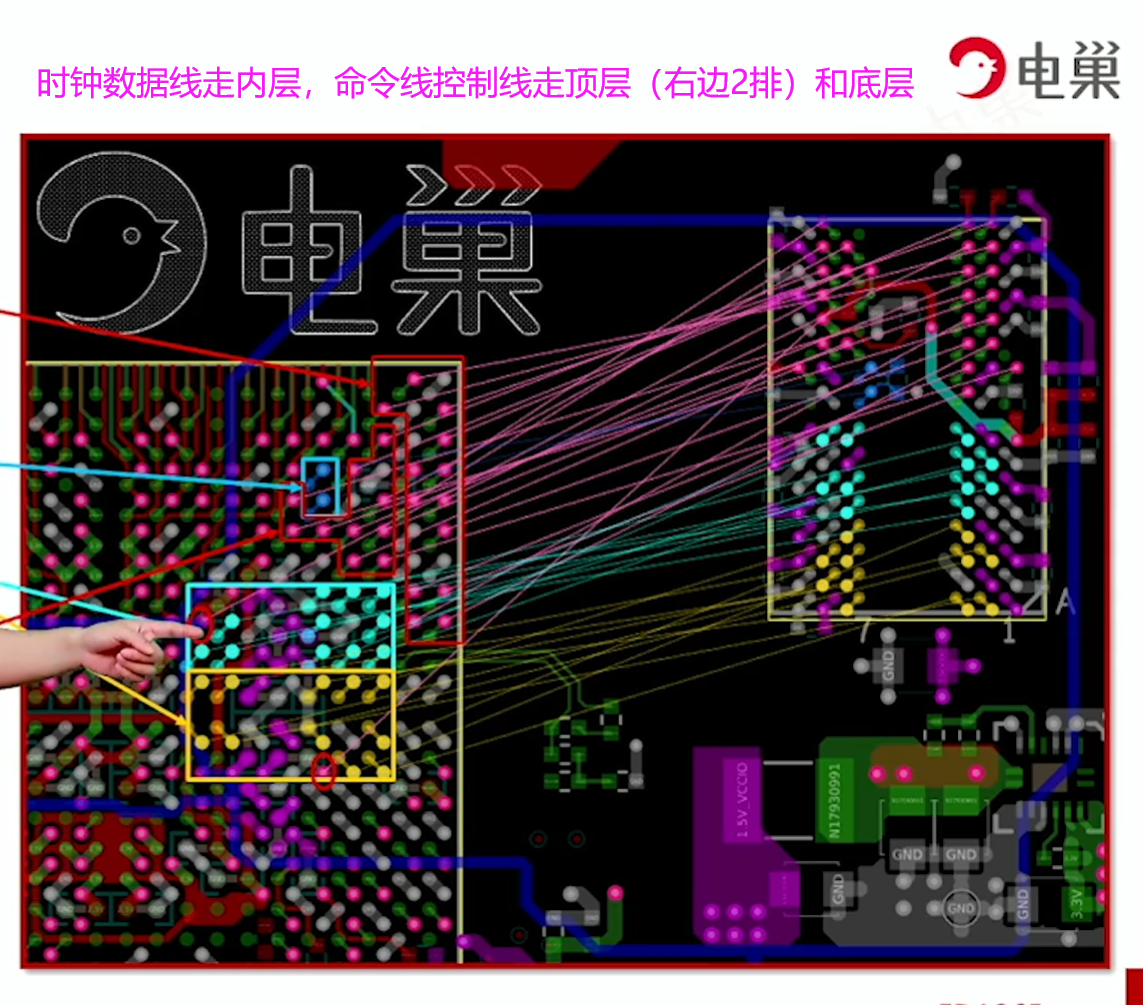

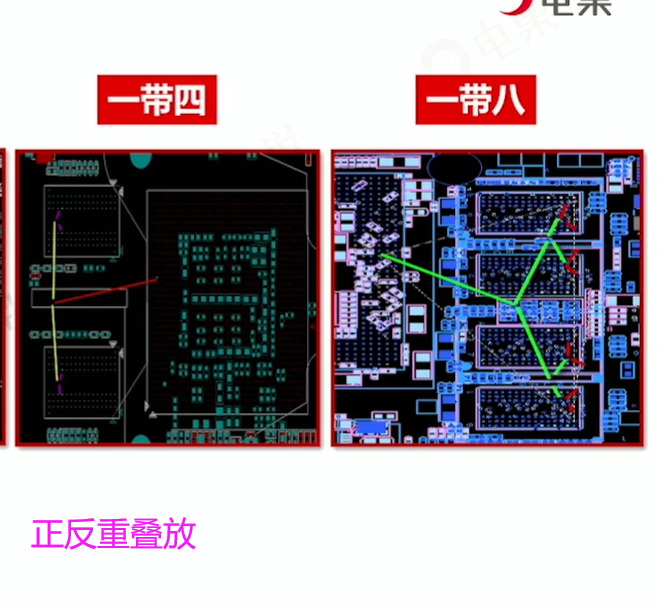

前两排都是地址/命令/控制信号直接顶层相连,FPGA的PIN脚可以互换;

时钟线2根走内层,两组数据线也走内层;

剩下的地址/命令/控制信号线走底层;

前两排都是地址/命令/控制信号直接顶层相连,FPGA的PIN脚可以互换;

时钟线2根走内层,两组数据线也走内层;

剩下的地址/命令/控制信号线走底层;

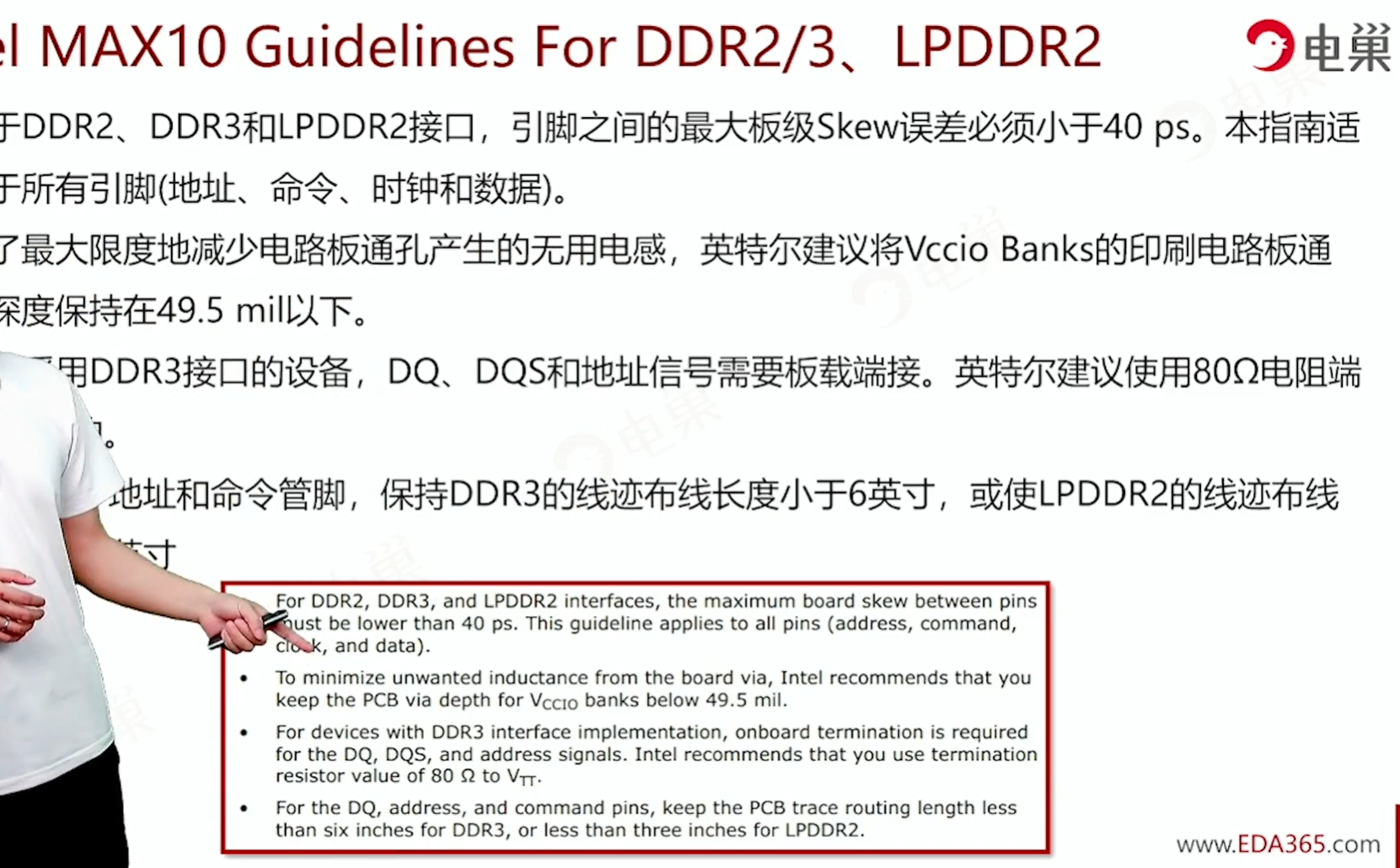

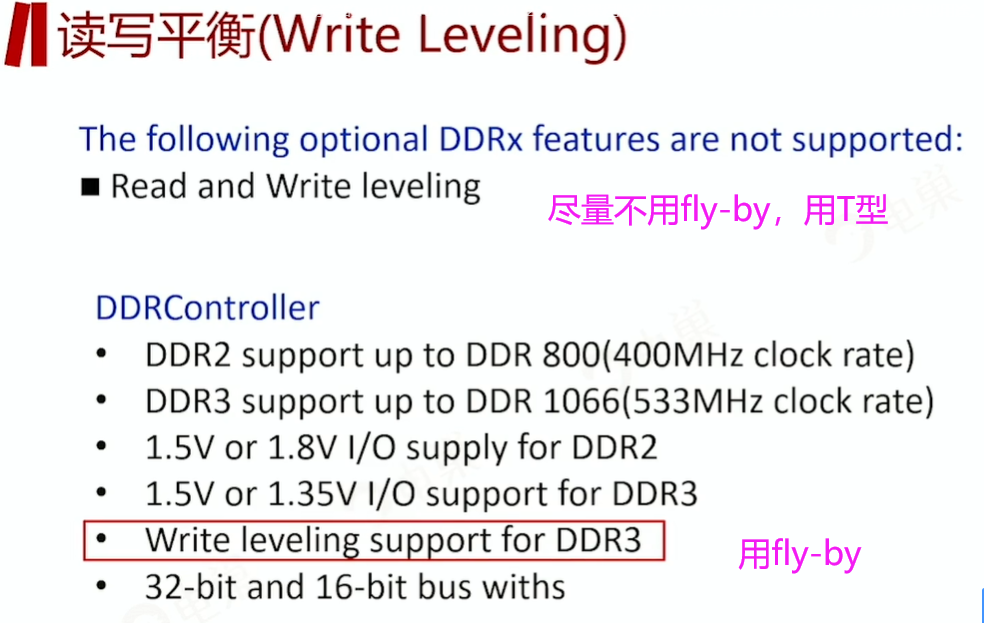

MAX10芯片要求:

1ps约估算为5mil;

数据线、时钟线参考地平面,地址命令线等可以参考DDR自己的电源平面

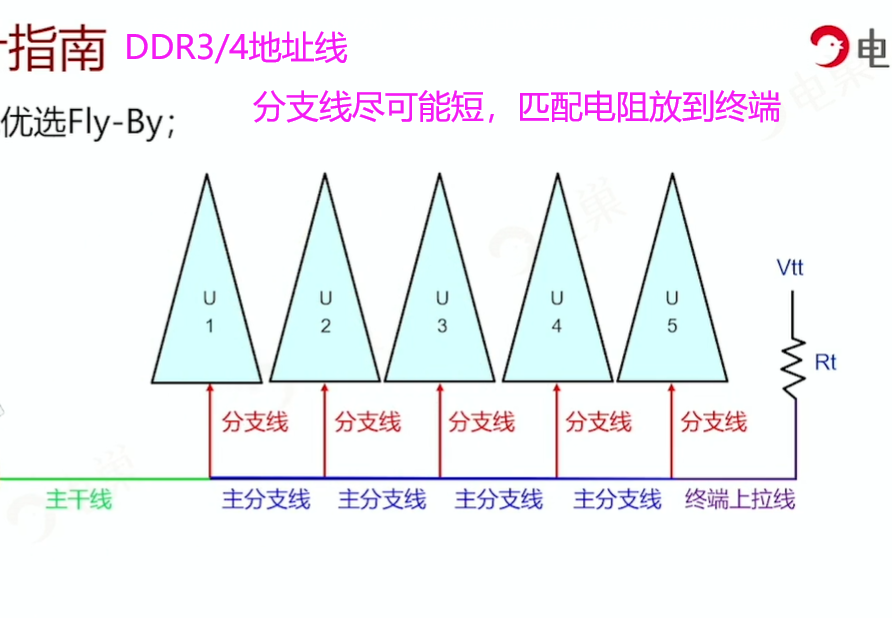

flyby拓扑布线参考:

8片打孔在DDR中间位置

flyby拓扑最后一个波形是最好的,第一个是最差的;

端接电阻阻值最好仿真确定,参考设计39Ω/60Ω仅供参考;

必须考虑地址命令走线长度,以便与时钟的飞行时间偏差相匹配;

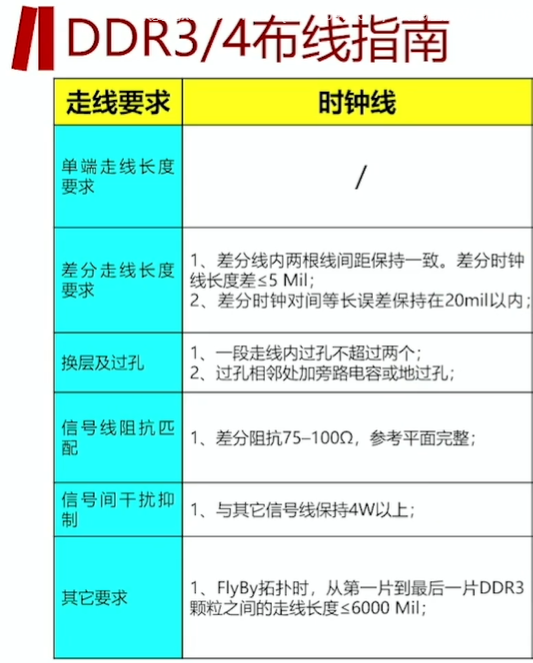

没有厂家参考设计参数时,以下内容可供参考,不一定非要按照数据误差设计:

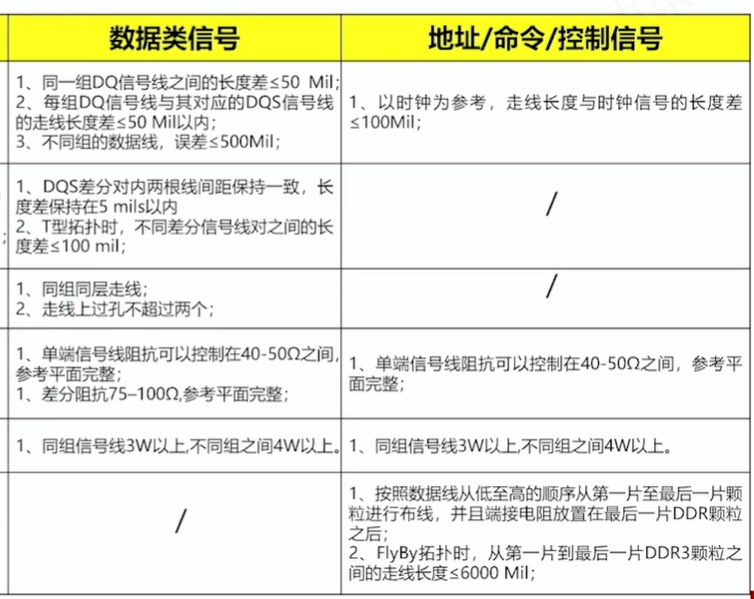

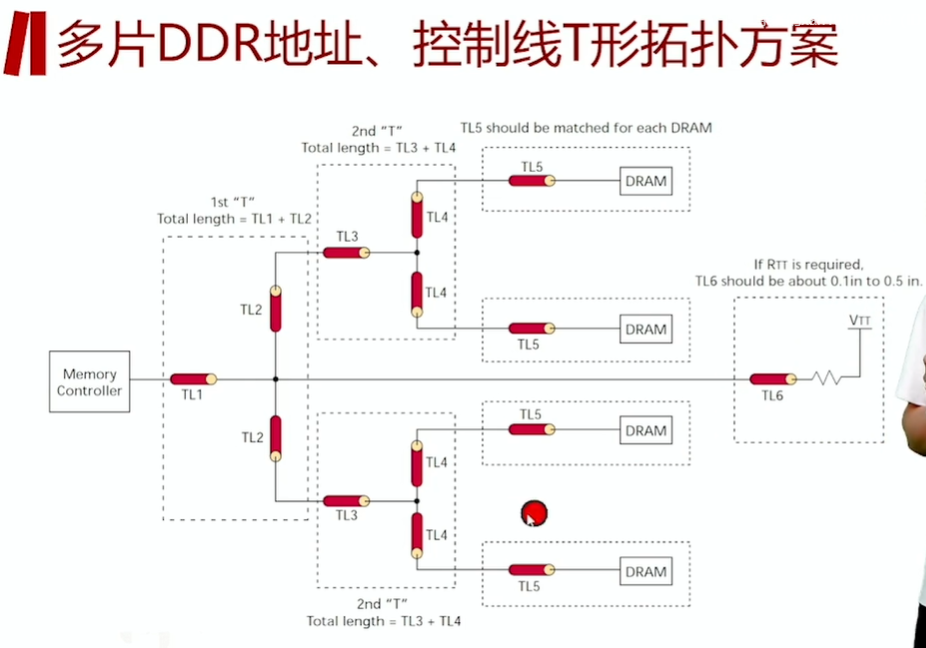

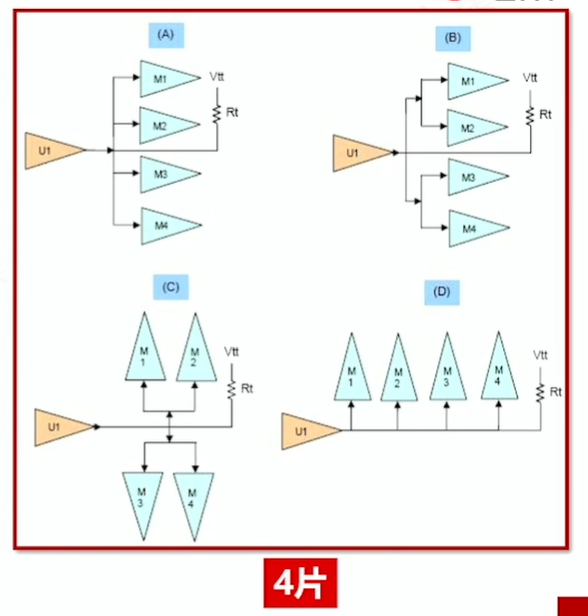

四片DDR地址控制线T形拓扑:

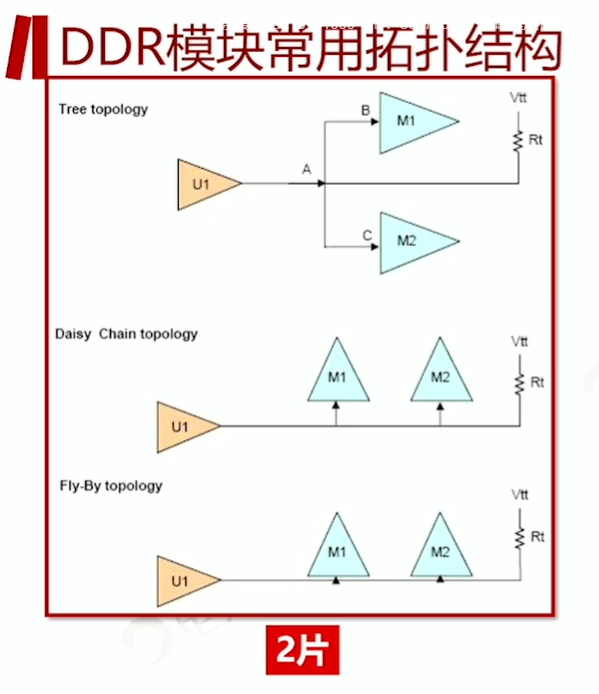

拓扑结构选择:

BANK组容量翻倍

POD电平:

数据总线倒置(DBI):

让高电平尽可能多,降低DDR4功耗

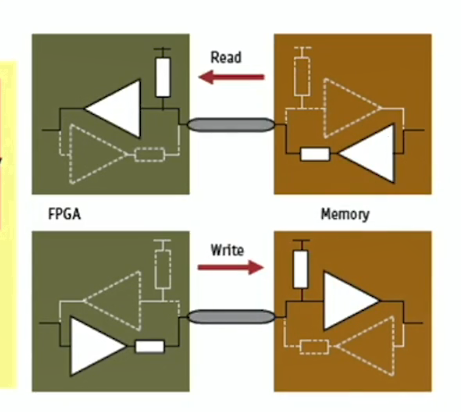

读写平衡是在DDR颗粒端

ODT:

将匹配内置到芯片中,提高数据总线的信号质量

动态ODT:

进一步提高DDR3数据总线的信号质量,特别是多个负载,例如:双内存条系统中

拓扑结构:

小于4颗用T型或者FLY-BY差别不大,多余4颗甚至8颗以上FLY-BY效果会好很多

预取架构:

存储器:

RAM(随机存储器)、ROM(只读存储器)

RAM(随机存储器):

SRAM(静态)、DRAM(动态)

时钟、复位等重要信号线间距至少3W以上,差分线和其他信号线的距离≥20mil

降低反射:

差分线对内间距、失配长度等;

过孔要符合加工要求,超高速信号时过孔规格还要通过仿真确定;

通过软件控制走线、过孔、铜箔等之间的间距;

约束过孔数量,控制返回路径;

时序等长约束;

降低串扰的措施:

增加信号路径之间的间距;

使耦合长度尽量短;

在带状线层布线;

用平面作为返回路径;

减小信号路径的特性阻抗;

使用介电常数较低的叠层;

在封装和接插件中不要共用返回引脚;

使用两端和整条线上有短路过孔的防护布线(包地+均匀过孔);

降低信号上升/下降沿时间。

串扰只能降低不能消除,只是噪声的一部分

每条线上的总串扰来自于多个串扰源的串扰,所有串扰累加起来达到了最大值

3W原则:

前提条件是满足50欧姆阻抗或者说是满足同一个阻抗要求。

重要信号线(时钟、复位、高速差分等)使用3W规则,其他普通信号线不是必须要求。

满足3W原则减少70%线间干扰,满足10W原则减少98%线间干扰。

高速PCB规则:

板材、叠层、线宽、间距、线长、等长、回流、拓扑、过孔、载流、PDN。

接口模块摆放:

先防护后滤波,差分线需要交换时要整组交换,接口模块靠近接口摆放。

核心芯片模块摆放:

DDR1/2推荐T型拓扑摆放,匹配电阻放在T点;

DDR3/4按照Fly-By摆放,末端匹配电阻靠近末端存储芯片,匹配电阻到末端存储芯片布线长度≤500mil;有的DDR3主芯片不支持读写平衡的话,还是采用T型拓扑。

电源模块摆放:

远离易受干扰电路,如ADC、DAC、RF、时钟等电路模块;

专用电源靠近负载摆放。

布局优化:

优先保证关键(时钟线、高速线、模拟、射频)顺畅最短。

将功能模块定义成一个group,方便调整布局快速移动、旋转等操作

高速PCB叠层不仅指定PP类型、树脂含量还要指定芯板规格