90年代的时候,外围高速总线的频率还在66MHz左右,那时候八层板算是复杂度很高的单板,那时候介质材料的Dk和Df很高,设计裕度很宽,很少人关心铜箔和玻纤的特性,基本所有的PCB材料都叫“FR-4”,因为板材的电气性能对信号质量影响不大。

通信技术近十几年来的快速演变,从1G、2G一直演变到现在的5G,信号速率和频率都成倍的增加,以PCI总线为例,技术已经从20年前的一代演变到现在的六代,速率整整提升了25倍,总线速率已经达到了64Gbps.

随着信号传输速率和频率都越来越高,影响信号完整性的关键因素现在不仅包括阻抗,还包括损耗、铜箔粗糙度和玻纤编织效应等,PCB叠层设计变得越来越不容忽视,每一个叠层的细微差异都可能影响信号传输质量。

事实上,在物理世界构建PCB的过程中发生的一切都会或多或少的影响信号质量,因此需要考虑的细节不仅仅是一个PCB叠层本身,而是涉及每个PCB制造商的叠层加工过程。

PCB叠层问题是造成PCB改版的最常见的原因之一。不良的PCB 叠层设计会导致传输线阻抗失配,参考平面缺失等,并引起严重的信号完整性问题;电源和地层的不合理安排也会引入大量回路电感,引起去耦电容的“失效”;同时叠层设计也是影响EMI/EMC 的重要因素。

如何才能设计出满足高频高速PCB要求的叠层,最大的挑战是如何建立有效的叠层模型,包括:铜厚、层压后的厚度、DK、DF、玻纤结构等。如果没有准确的叠层模型,将无法在设计初期进行准确的信号完整性仿真,这样制造出来的实际产品就很难符合预期性能。

7月28日晚20:00电巢直播邀请到了西门子EDA亚太区EBS技术专家季伸彪及国内知名企业高速设计专家杜正阔,两位老师将从通信通讯行业应用案例来分析,为大家讲解如何在满足产品的需求下,合理进行PCB的叠层规划。

7月28日 周四

季伸彪、杜正阔

《西门子EDA通信通讯行业应用案例 基于ZYNQ7045电子系统硬件设计Ⅲ》

1、直播内容简介

本场直播,我们将结合ZYNQ7045板卡,来展示如何设计满足仿真需求的有效叠层模型,其中包含:

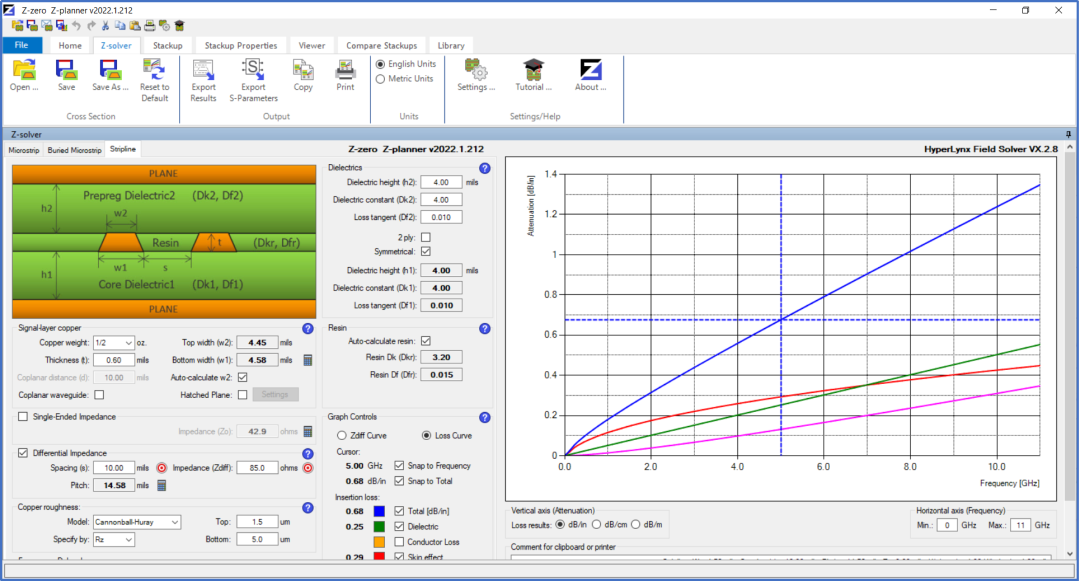

·如何计算满足产品阻抗要求的差分线配置

·如何根据损耗要求选择合适的板材和设计约束

·如何权衡性能和成本,选择合适的板材

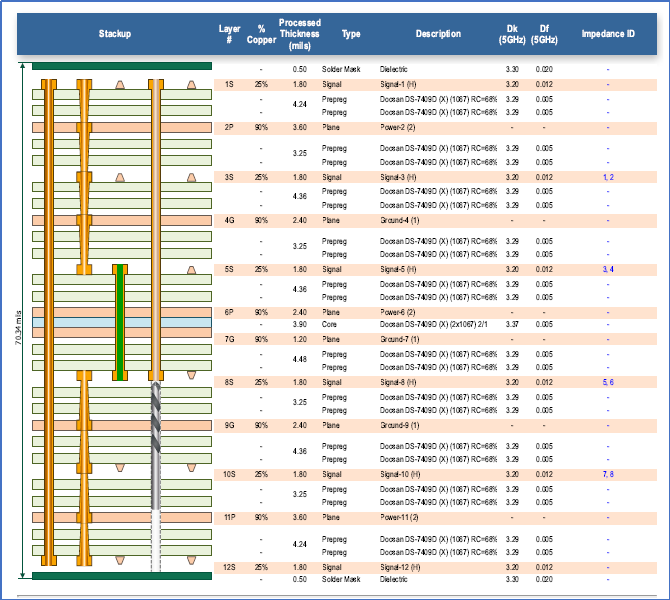

·如何快速创建有效的高速PCB叠层模型

·如何对不同供应商的叠层进行快速验证

·如何无缝将叠层模型轻松的导入仿真工具

2、讲师介绍

杜正阔老师:

原国内知名企业高速设计专家

EDA365 cadence allegro论坛特邀版主

20多年高速PCB设计、仿真经验。曾任港湾网络、一博科技、兴森快捷等高科技企业工程师、高级工程师、设计经理等职务,设计过的产品涵盖通信、医疗、工控、计算机、雷达、消费类等多个行业。

个人主要出版物:

《Cadence Allegro 实战攻略与高速PCB设计》

季伸彪:

西门子EDA亚太区EBS技术专家

2019年加入Siemens EDA, 加入Siemens EDA之前曾经在国内大型EMS公司及国内知名通讯公司任职,深刻了解PCB设计与制造过程中的可制造性要求,熟悉PCB叠层的设计与制造的各项参数,2006年开始从事可制造性相关技术岗位。

3、直播要点

1、高速PCB叠层设计方法与技巧

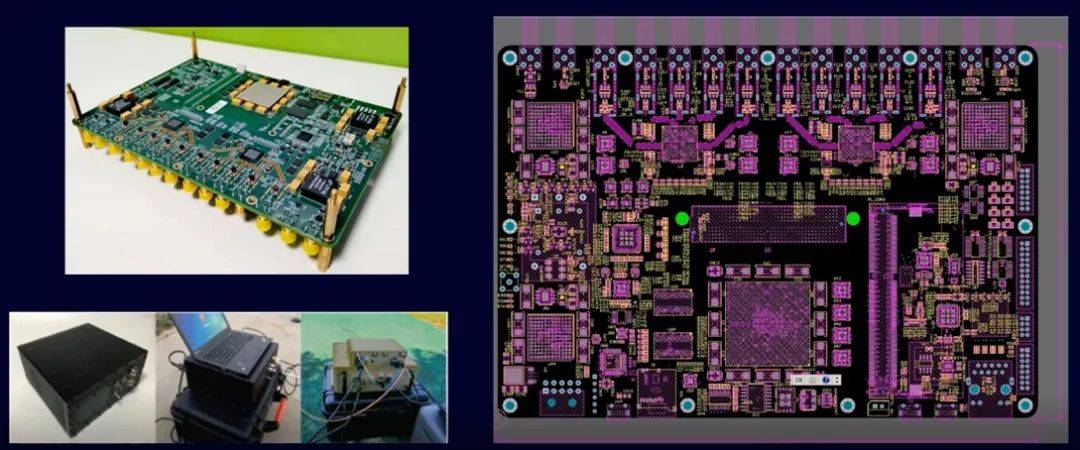

2、结合ZYNQ7045板卡,进行叠层规划

3、叠层设计如何影响信号完整性

4、结合ZYNQ7045板卡,使用Z-planner Enterprise进行叠层设计演示

PCB设计中的叠层设计

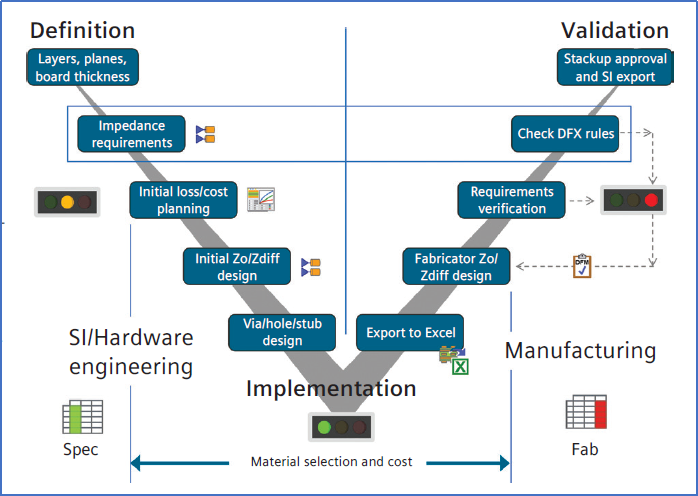

叠层设计在高速应用中变得非常重要,叠层的设计包含多个方面:如何定义层叠设置,如何计算阻抗和损耗,如何选择材料,如何获取有效的材料参数(铜箔、材料),如何与PCB板厂建立有效的叠层沟通等等

好的叠层设计流程可以极大提高设计团队效率,节省大量的时间和成本。

PCB设计中的叠层设计

基于ZYNQ7045板卡的阻抗与叠层设计案例

基于Siemens EDA的Z-planner Enterprise和ZYNQ7045板卡的损耗及阻抗需求,手把手从阻抗计算、损耗模拟、材料选择与对比、叠层创建一直到供应商叠层验证,进行全流程的叠层设计演示。

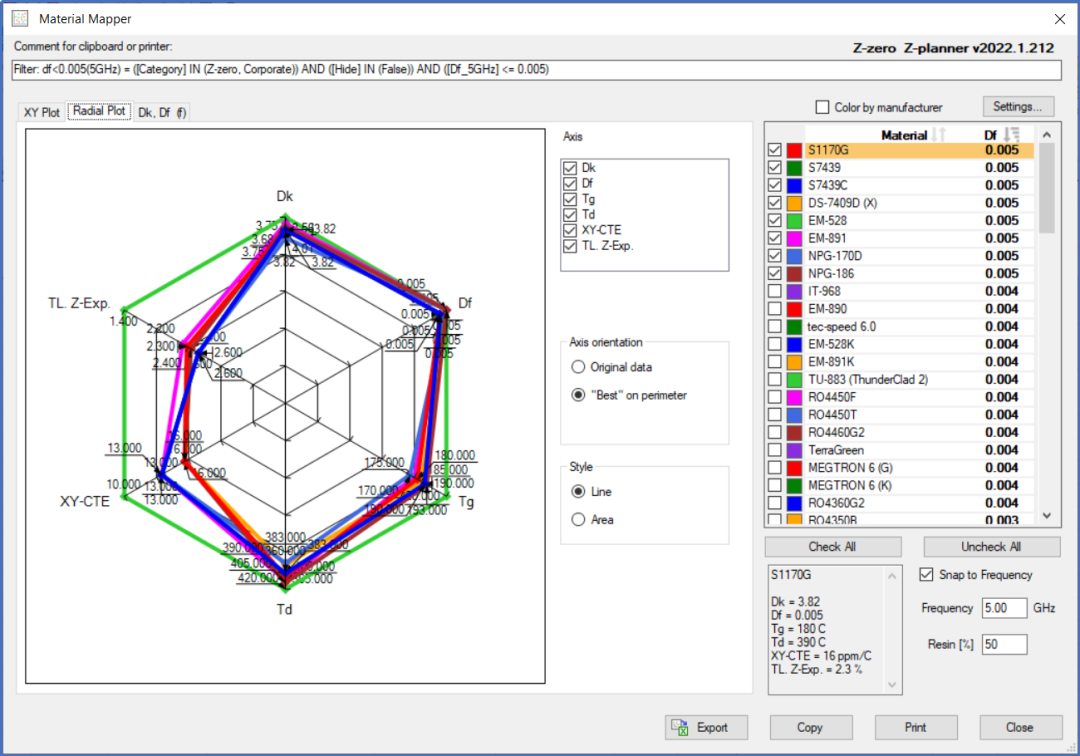

高速PCB板材库

高速PCB叠层设计中最重要的环节就是PCB材料选择,目前Z-planner Enterprise集成了欧美以及亚太地区常用的板材供应商的材料库,包含185多个系列的板材数据,可以满足不同客户对PCB材料的需求。这些数据均来自全世界主流的制造商,包括但不仅限于AGC、Isola、EMC、斗山、ITEQ、南亚、松下、生益、TUC、Rogers、Dupont和Ventec。

这使得在选择材料时,用户可以充分考虑基于不同频率下的不同玻纤结构的Dk、Df等参数, Material Matching功能可以根据所选的材料参数快速替换和更新叠层设计,并提供全面的雷达图,包括Dk、Df、Tg、Td、z-CTE和x-y CTE等参数。

Z-Planner Enterprise集成主要层压板制造商材料库,您可以随时随地在材料库中调用各种材料参数

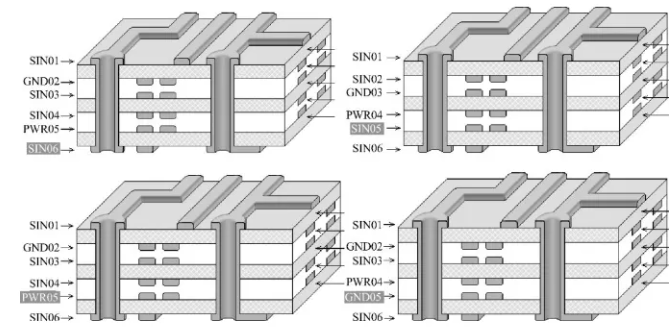

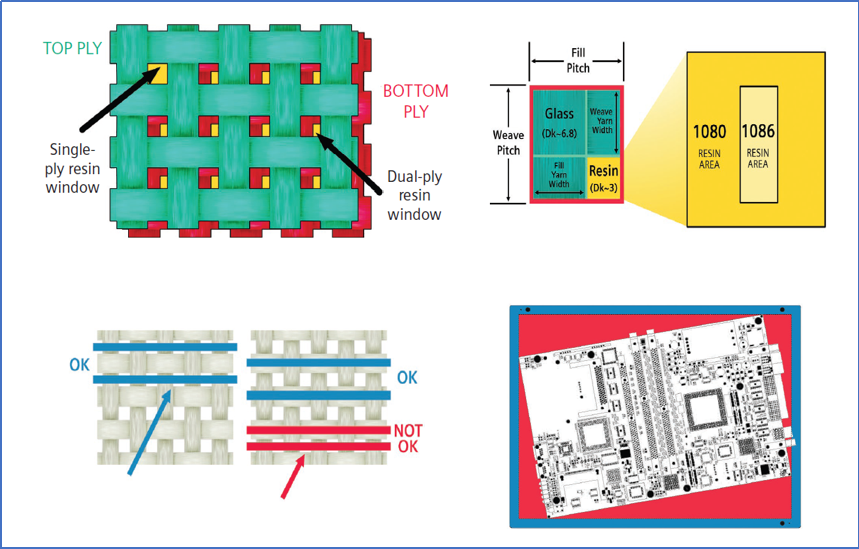

常见的玻纤编织效应的缓解方法

纤维编织效应,是印刷电路板(PCB)中经常被忽视但会影响差分时序的来源之一。如何低成本、高质量的减轻玻纤编织效应是高速叠层设计无法绕开的话题,如何将常见的玻纤编织效应缓解方法引入叠层设计中也尤为重要。

部分玻纤编织效应缓解方法

4、适合对象

通信通讯行业从业者

项目经理

硬件工程师

PCB工程师

SI/PI工程师

DFM工程师

- 还没有人评论,欢迎说说您的想法!